各位专家:

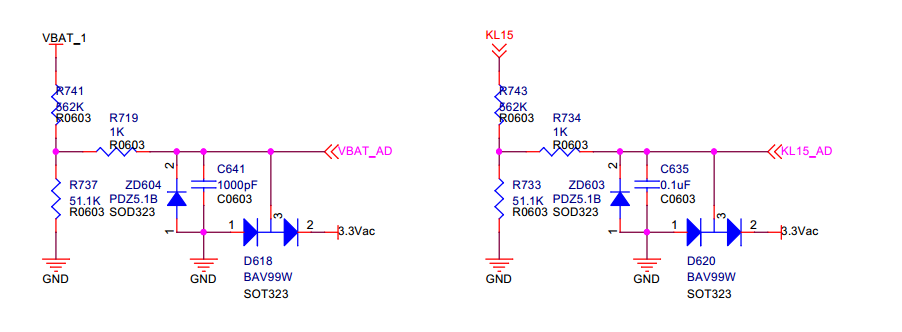

客户想知道是否需要优化 ADC 采样硬件、例如降低 R741和 R743值、因为在以下情况下会发生异常现象。

如下图所示、当将12V 直流电源同时置于 VBAT_1和 KL_15时、两个具有相同结构和元件的采样电路

1) 1)将 VBAT_AD 和 KL15_AD 引脚与 MCU 连接、一个 ADCResult 为1210、另一个为1224、VBAT_AD 和 KL15_AD 的值对应于相关的 ADCResults 值、但实际的 ADCResults 值与理想结果值1241相比有很大的差距。

2) 2)当与 MCU 断开 VBAT_AD 和 KL15_AD 引脚时、VBAT_AD 和 KL15_AD 电压正确。

3) 3)根据客户的要求,由 ADCResult 计算的 VBAT_1和 KL_15值的误差应限制为0.2V,反映在 ADCResult 误差为21 LSB。

请就此问题提供一些建议、谢谢!

ADC 采样电路

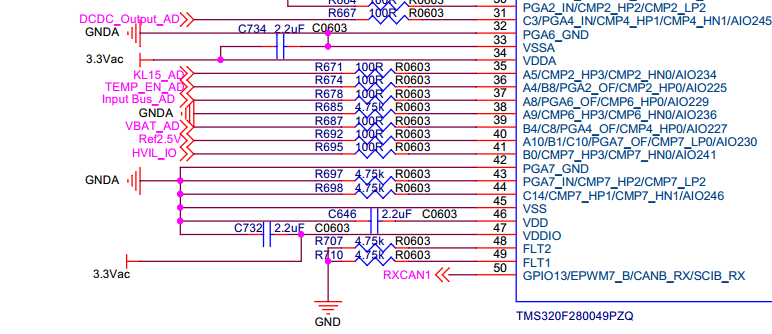

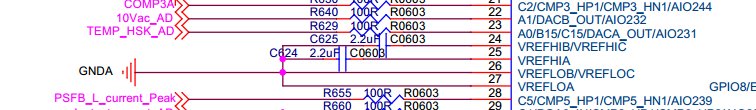

引脚映射 图

-王雷娜