您好,

我的客户使用 C28346。

使用 EMIF 访问 CPLD 时出现问题。

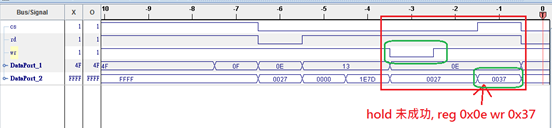

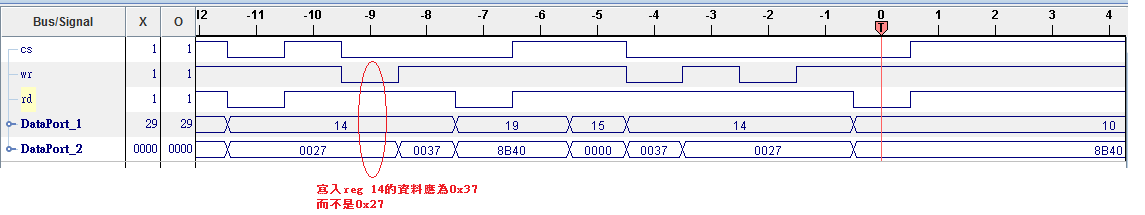

问题是 /WR 信号与数据总线不同步。

它希望将0x37写入 CPLD。

但实际上,它会将旧数据0x27写入 CPLD。

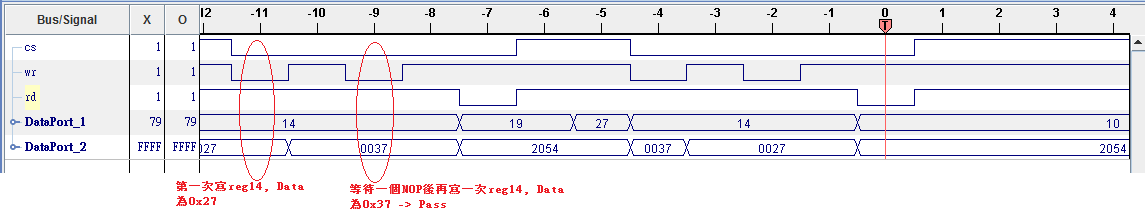

将"NOP"添加到故障代码后、结果是正确的。

问题1:导致/WR 信号与数据总线不同步的原因是什么?

问题2: 正确的解决方案是什么?

谢谢、

此致、

Simen

------ ----------------------------------------------------

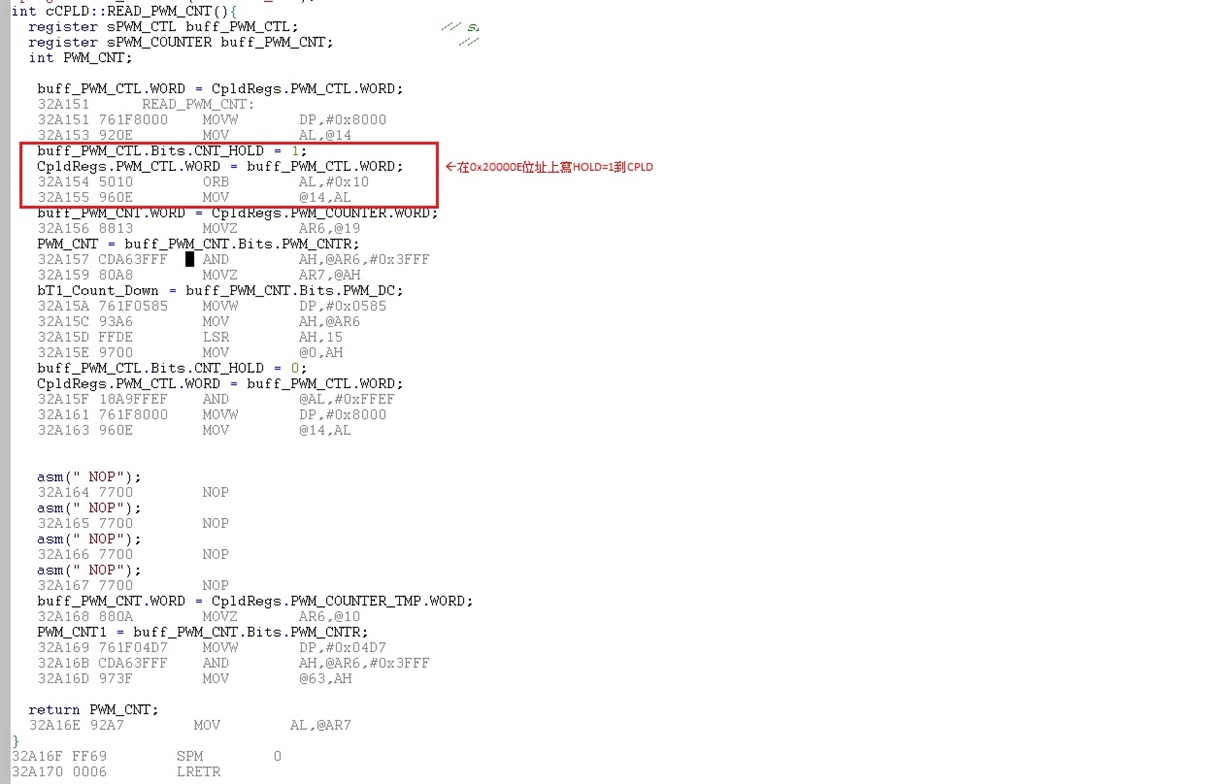

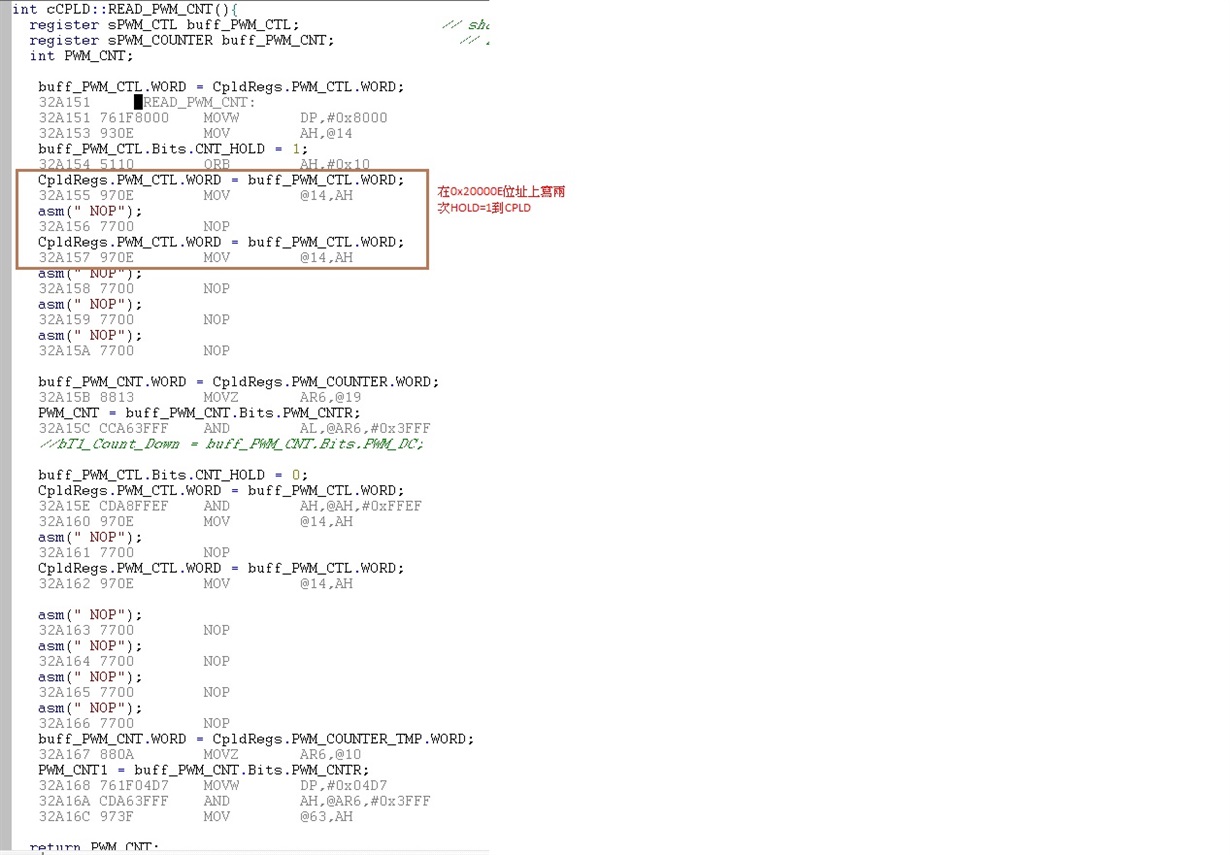

寄存器 sPWM_CTL buy_PWM_CTL;

寄存器 sPWM_COUNTER buy_PWM_CNT;

int PWM_CNT;

buff _pwm_CTL.word = CpldRegs.PWM_CTL.word;

缓冲器_pwm_CTL.Bits。CNT_HOLD = 1;

CpldRegs.PWM_CTL.word = buw_PWM_CTL.word; <--写入 保持=1到位于0x20000E 地址的 CPLD

buff _pwm_cnt.word = CpldRegs.pwm_counter.word;

PWM_CNT =缓冲器_pwm_CNT.Bits、PWM_CNTR;

缓冲器_PWM_CTL.Bits。CNT_HOLD = 0;

CpldRegs.PWM_CTL.word =缓冲器_pwm_CTL.word;

--------------------------------------------------

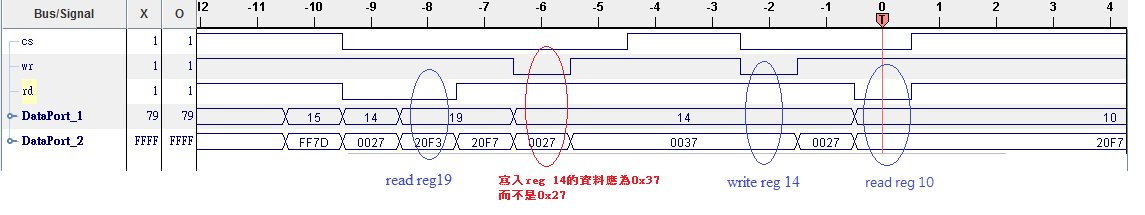

故障代码波形:(保持未成功,寄存器0x0E WR 0x37)

------ ----------------------------------------------------

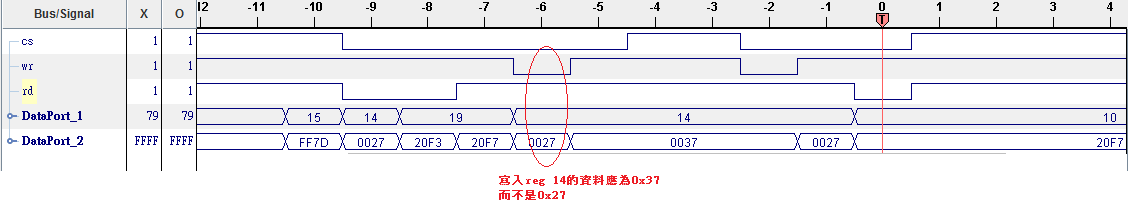

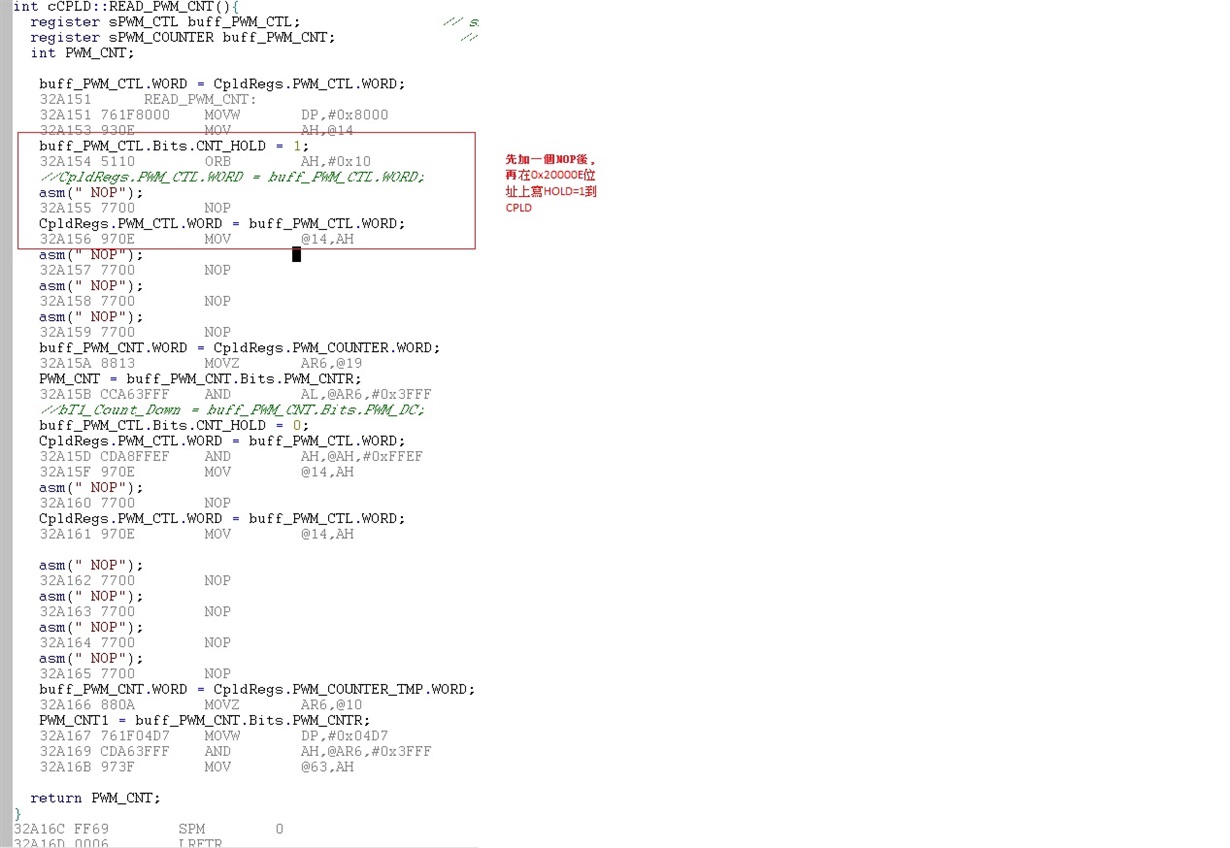

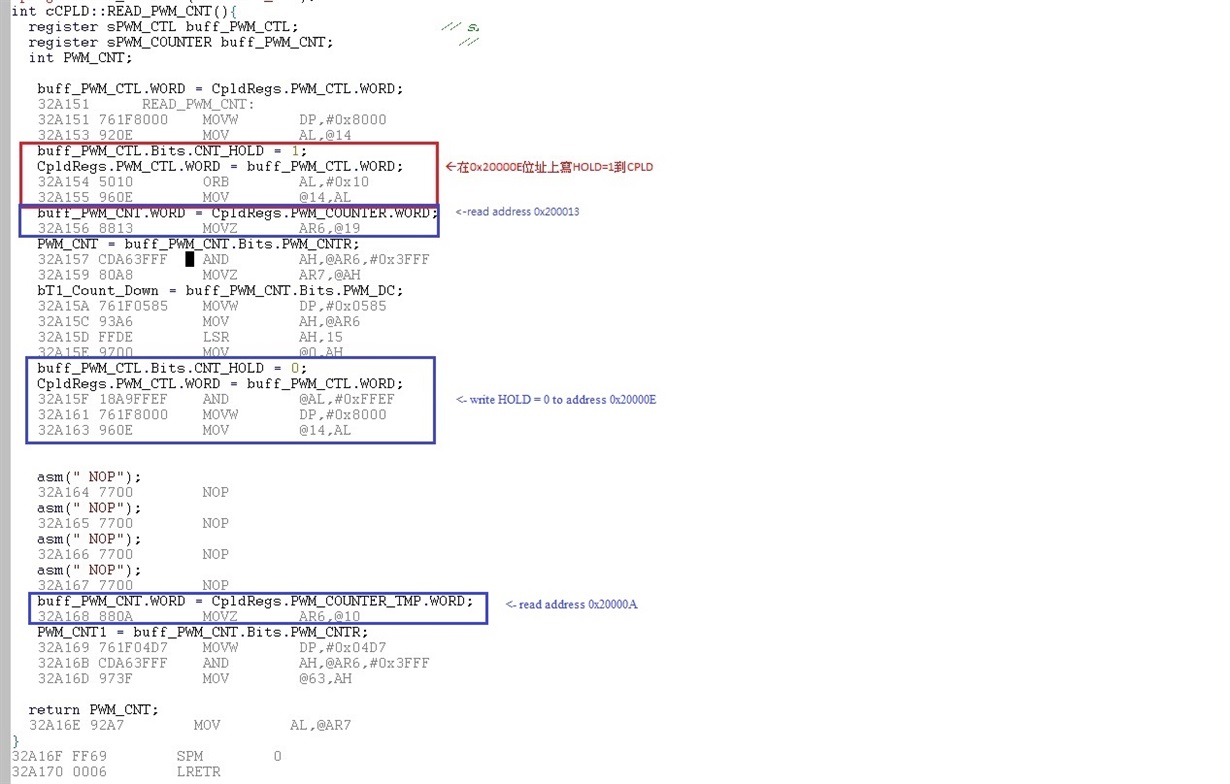

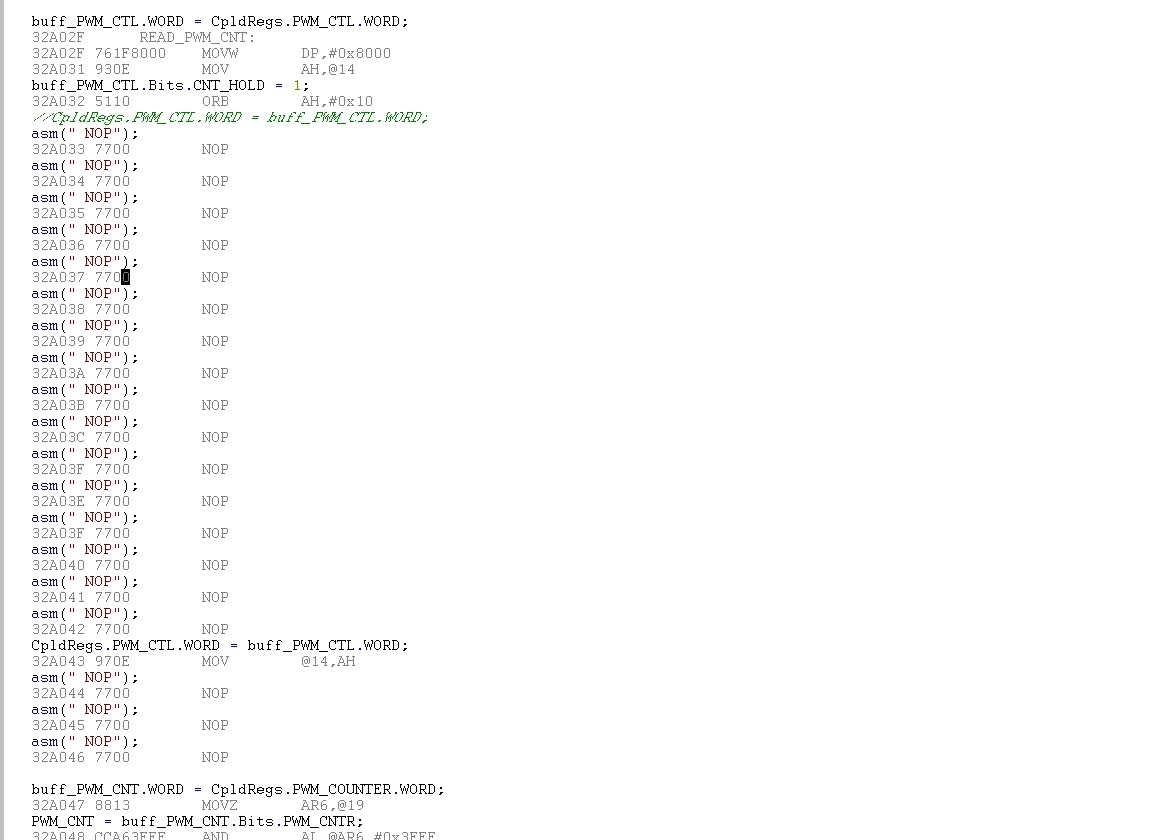

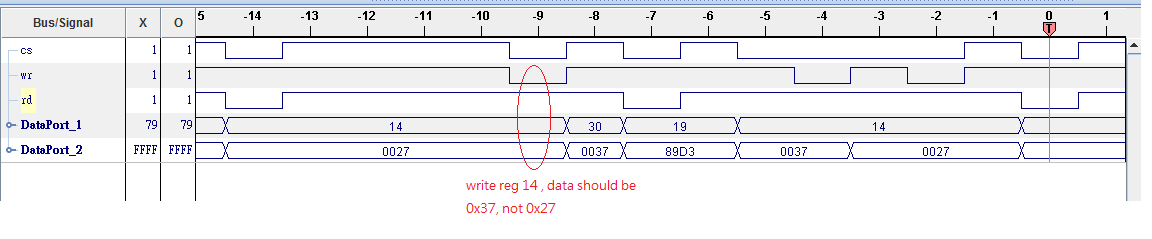

寄存器 sPWM_CTL buy_PWM_CTL;

寄存器 sPWM_COUNTER buy_PWM_CNT;

int PWM_CNT;

buff _pwm_CTL.word = CpldRegs.PWM_CTL.word;

缓冲器_pwm_CTL.Bits。CNT_HOLD = 1;

CpldRegs.PWM_CTL.word =缓冲器_pwm_CTL.word;

asm (" NOP");

CpldRegs.PWM_CTL.word = buw_PWM_CTL.word; <--写入 保持=1到位于0x20000E 地址的 CPLD,并且它成功

asm (" NOP");

asm (" NOP");

asm (" NOP");

buff _pwm_cnt.word = CpldRegs.pwm_counter.word;

PWM_CNT =缓冲器_pwm_CNT.Bits、PWM_CNTR;

缓冲器_PWM_CTL.Bits。CNT_HOLD = 0;

CpldRegs.PWM_CTL.word =缓冲器_pwm_CTL.word;

asm (" NOP");

CpldRegs.PWM_CTL.word =缓冲器_pwm_CTL.word;