主题中讨论的其他器件: TMDSCNCD28069

你好。 每个人。

我对 TMS320F28069的 HRPWM 有疑问。

当通过向 PWM1添加相位差来操作 PWM2时、在相位差中、PWM2的输出定期成为跳周期。 *1.

如何摆脱 PWM2输出跳周期?

*发生跳频的1相位值(EPwm2Regs.TBPHS.ALL)

0x00AE9800至0x00AEFF00

0x00AF2000到0x00AFFF00

0x00B02000到0x00B07700

正常波形

黄色:PWM1A、青色:PWM1B、品红色:PWM2A、绿色:PWM2B

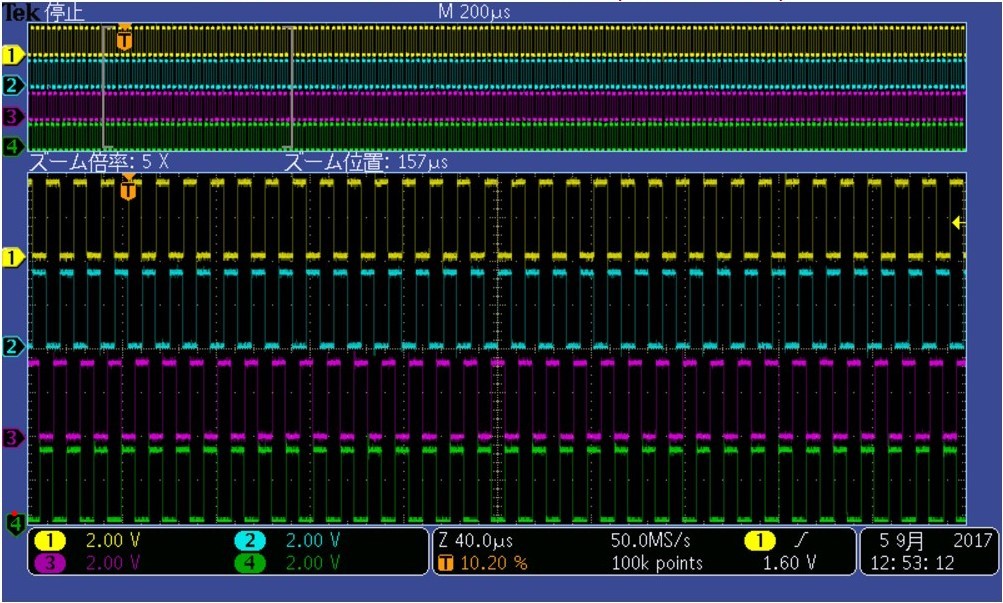

非法波形

黄色:PWM1A、青色:PWM1B、品红色:PWM2A、绿色:PWM2B

可以立即发送项目文件。

此致、

Maekawa