主题中讨论的其他器件:LAUNCHXL-F28027F

您好!

我将与客户讨论 SW 稳压器的 ADC 计划。

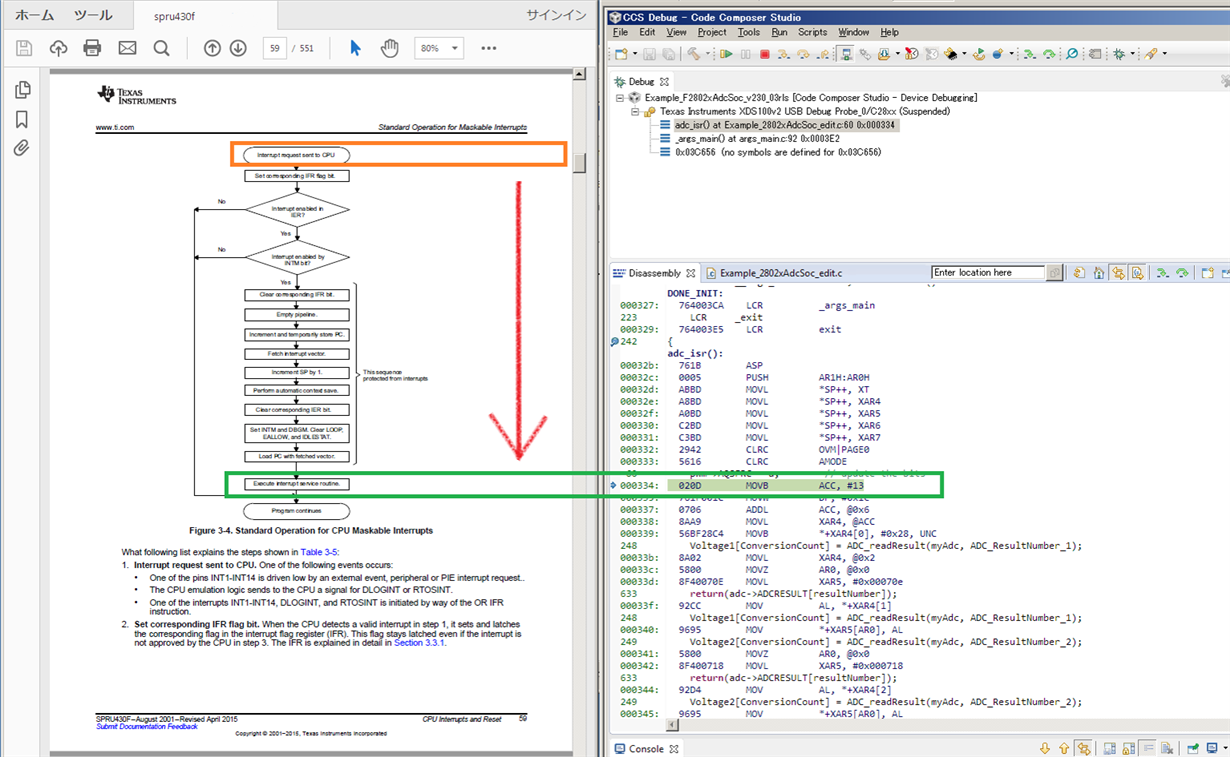

作为测试、我尝试了单个 ADC。 时间是1213nsec。

480nsec 用于 ADC 首次转换、因此剩余733nsec 将是开销。

您能告诉我733nsec 开销是否可以接受?

我为 CCS612添加了结果 XLS 和测试代码。

:基本示例代码= example_F2802xEPwmUpAQ v230

:编译器优化= 3.

:tSTART=(ePWM1.TBCTR=10),cmpA,pwmB=set,GPIO1=RISE。

:tSTOP =(我的 ADC ISR 条目代码)

:板= LaunchXL-F28027F

:INTOSC1=10MHz、SYSCLKOUT=50MHz、ADCCLK=50MHz (只要从代码中进行研究)

P.S. 我特意忽略了第1个样片问题以查看开销。

/cfs-file/__key/communityserver-discussions-components-files/171/170920e-Test-result-2rls.xlsx