您好!

我和 Nima Eskandari 交谈、但线程已关闭、因此我尝试提出这一相关问题。

你好、Nima、我在这里再次打扰你... 我希望我们可以重新打开线程!

要继续处理中断问题、"TMS320F28379D:TBCTR = CMPA 且 TBCTR = CMPB 上的 EPWM 中断"、

我已经使我的测试和你的想法运行良好、但是我发现我也可以使用 ePWMxA 上的周期和 ePWMxB 上的 CMPB 来生成我需要的中断。 看起来更简单...

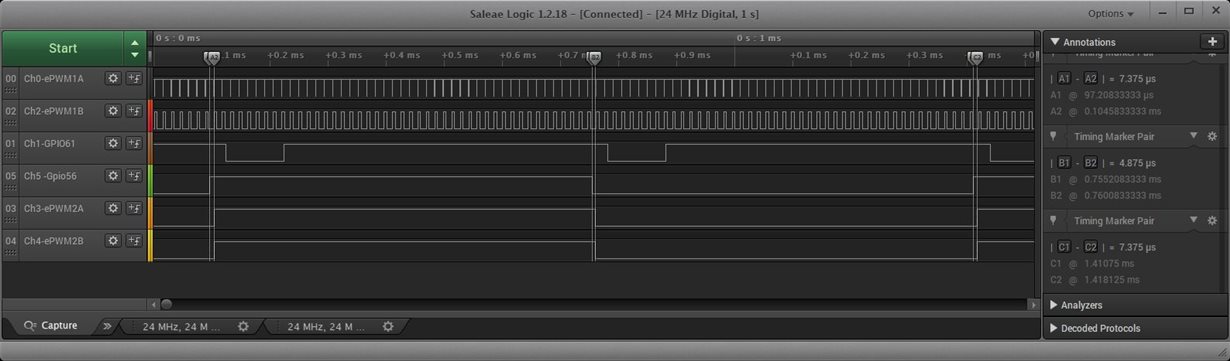

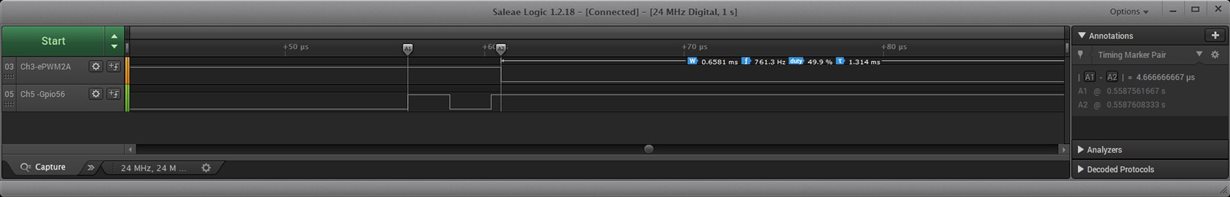

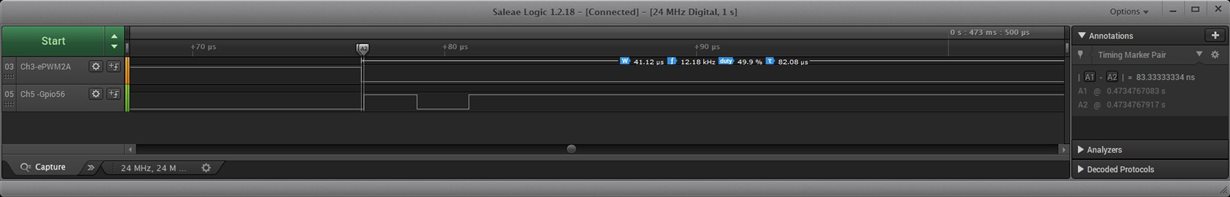

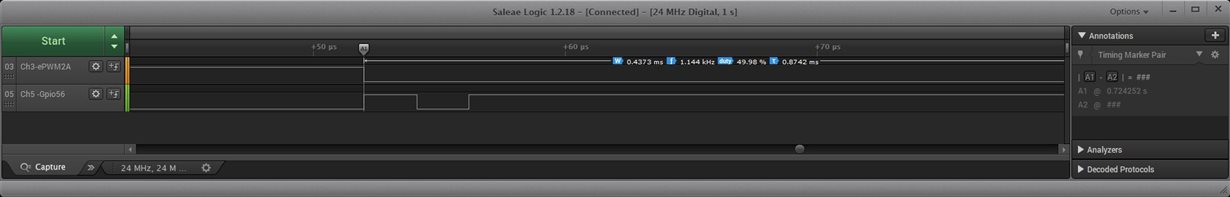

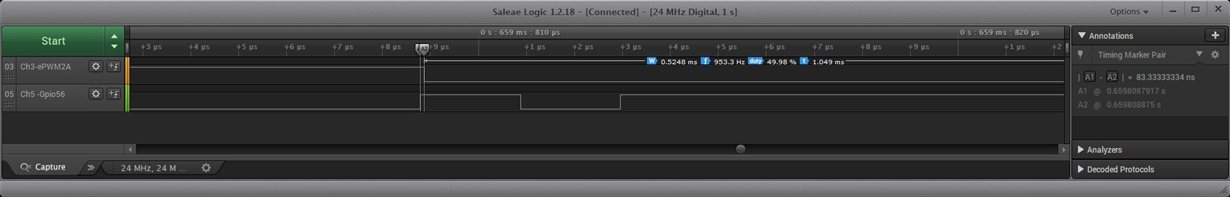

但是、时序不符合我的预期:

ePWM2上的中断 A 和 B 应该激活 ePWM1上的中断、这会在 ePWM1的 A 引脚变为高电平后将 GPIO56引脚清零为低电平。

理想情况下、这应该在大约5 us 后发生、但这并不是那么重要、只要这种情况保持不变。

中断工作、但时序不工作。

GPIO56会在任何时候变为低电平、但不会在我需要的那一刻变为低电平。

我的逻辑分析仪还显示、在 ePWM2输出 A 变为低电平或高电平之前、ePWM2的中断通信大约(随机) 4到7us、

虽然我只是在这个时间或稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍稍

我有两个问题:

1 -为什么中断比它应该到达的时间早得多?

到目前为止、这对我的应用不是很令人不安、但:

2 -为什么 Pin56会在时间上随机降低?

我知道、在调用 ISR 之前、有大约14个 SYSCLK 的传播延迟、但这并不能解释这种行为。

包含代码的 TE 相关部分。

我希望你度过一个美好的周末,或者,更好的,一个美好的周末!

Gustavo