尊敬的团队:

我有一位客户使用 XINTF 接口与 FPGA 进行通信、但无法写入数据。 下面是详细说明:

XINTF 配置如下:

void InitXintf (void){ //这显示了如何写入 XINTF 寄存器。 这里使用的//值是复位后的默认状态。 //不同的硬件需要不同的配置。 //有关与 // F28335 eZdsp 一起使用的 XINTF 配置示例,请参阅 examples/run_fin_XINTF 项目。 //对 XINTF 时序的任何更改只能由 在 XINTF 之外运行的代码//进行。 //所有区域------------------------------------------------------- //基于 XTIMCLK = 1/2 SYSCLKOUT EALLOW 的所有区域的时序; SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1; EDIS; EALLOW; XintfRegs.XINTCNF2.bit.XTIMCLK = 1; //没有写入缓冲 XintfRegs.XINTCNF2.bit.WRBUFF = 0; // XCLKOUT 被使能 XintfRegs.XINTCNF2.bit.CLKOFF = 0; // XCLKOUT = XTIMCLK/2 XintfRegs.XINTCNF2.bit.CLKDE=0;/--- //使用就绪时、有效的必须为1或更大 //引线必须始终为1或更大 //区域写入时序 XintfRegs.XTIMIG0.bit.XWRLEAD = 3; XintfRegs.XTIMIG0.bit.XTIWRARTIVRE=7; XintFREGS.XINGRMIRG.3 ;XTIMIG0=3;XTIMIRT.XINT.XTIMIRG0=7;XINT.XTIMIRG.XTIFREG=7;XINT.XINT.XTIMIRG.3;XTIFRTS=TID.XINT.XTIMIRG.3;TID.XING.3;TID.XINT.XINT.TIDRDIL.TID.T0 = 7;TIDRDIL.TID.T= //双倍所有区域读取/写入超前/主动/跟踪时序 XintfRegs.XTIMING0.bit.X2TIMING = 1; //区域将对 XREADY 信号 XintfRegs.XTIMING0.bit.USEREADY= 1;//修改值,忽略xready信号 XintfRegs.XTIMING0.0 = 1 ; //必须为异步大小= 1;//必须为0、XTIMIGN = 1;//必须为0 = 1;/ 0 = 1 / 0、XTIMIGN = 1

使用 ZONE0区域、通信代码如下:

void 通信 FPGA (void)

{

GpioDataRegs.GPACLEAR.bit.GPIO5=1; //D_G_A 使能A相数据总线收发器

GpioDataRegs.GPASET.bit.GPIO30 = 1; //D_G_B 禁止B相总线收发器导通

GpioDataRegs.GPBSET.BIO32 = 1; //D_G_C 禁止C相总线收发器导通

GpioDataRegs.GPACLEAR.bit.GPIO2 = 1; //a_G_A****地址线总线收发器使能,低电平使能

GpioDataRegs.GPASET.bit.GPIO1=1; B地址总线禁止_G_T Ü V

GpioDataRegs.GPBSET.BIO39 = 1; /A/A_G_C

GpioDataRegs.GPASET.bit.GPIO4=1; //D_DIR_A 总线收发器方向、DSP->FPGA

GpioDataRegs.GPASET.bit.GPIO3=1;

*(sendStart + 0)=值; //value = 9。

*(sendStart + 1)=值;

*(sendStart + 2)=值;

*(sendStart + 3)=值;

*(sendStart + 4)=值;

*(sendStart + 5)=值;

*(sendStart + 6)=值;

*(sendStart + 7)=值;

GpioDataRegs.GPACLEAR.bit.GPIO4=1; //D_DIR_A 总线收发器方向、FPAG->DSP

GpioDataRegs.GPASET.bit.GPIO3=1;

/* recfPGAmessage[0]=*(recStart + 0);//第一个子模块电压

recfPGAmessage[1]=*(recStart + 1);//第二个子模块电压

recfPGAmessage[2]=*(recStart + 2);//第三个子模块电压

recfPGAmessage[3]=*(recStart + 3);//第三个子模块电压

recfPGAmessage[4]=第四个子模块电压(recStart + 4);//μ s

recfPGAmessage[5]=*(recStart + 5);

recfPGAmessage[6]=*(recStart + 6);

recfPGAmessage[7]=*(recStart + 7);//第六个子模块电压

recfPGAmessage[8]=第七个子模块电压(recStart + 8);//μ s

recfPGAmessage[9]=*(recStart + 9);//第七个子模块电压

recfPGAmessage[10]=*(recStart + 10);//第八个子模块电压

recfPGAmessage[11]=第八个子模块电压(recStart + 11);//μ s

recfPGAmessage[12]=*(recStart + 12);//第八个子模块电压

recfPGAmessage[13]=*(recStart + 13);//第八个子模块电压

recfPGAmessage[14]=*(recStart + 14);//第八个子模块电压

recfPGAmessage[15]=*(recStart + 15);//第八个子模块电压*/

GpioDataRegs.GPASET.bit.GPIO5=1; //D_G_A 禁止A相数据总线收发器

GpioDataRegs.GPASET.bit.GPIO2 = 1; A禁止A相地址总线收发_G_T Ü V

返回;

}

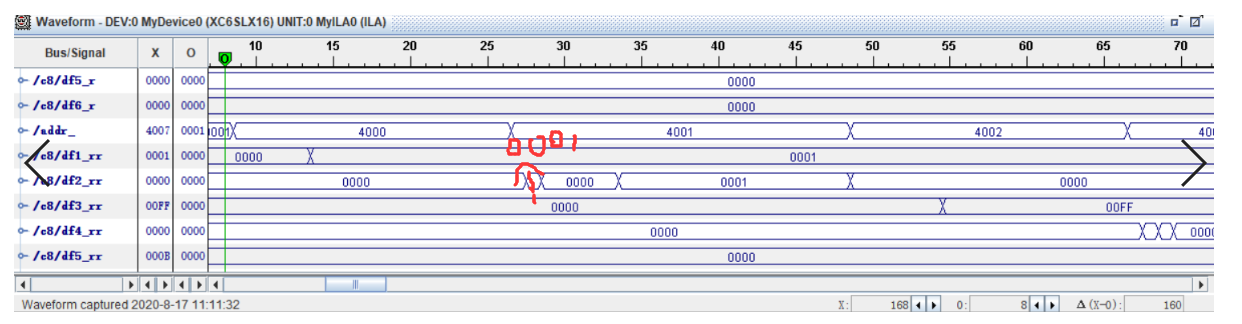

在仿真过程中、通过查看"Expressions"窗口、可以发现数据异常、没有模式。

我已经测试过 FPGA 时序是否正确。

什么可能导致问题?

此致