您好、香榭丽舍

我在这里询问我的客户。

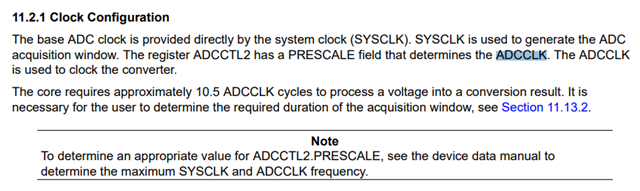

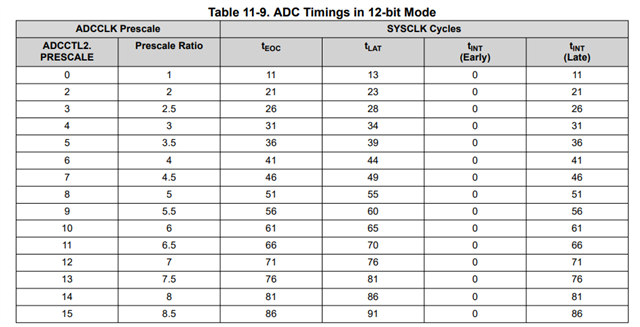

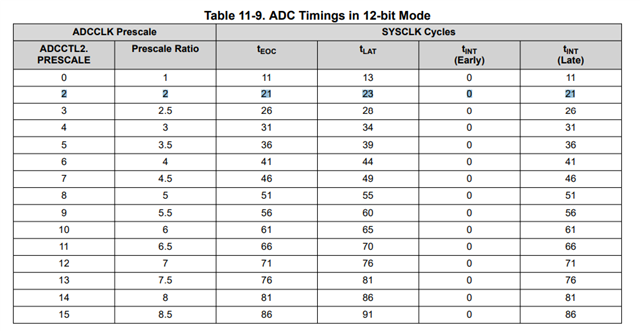

请帮助理解 ADC 时钟的频分设置基础、如下图所示? 如何选择 ADC 时钟的频率分频? 设置不同 ADC 时钟的用途是什么?

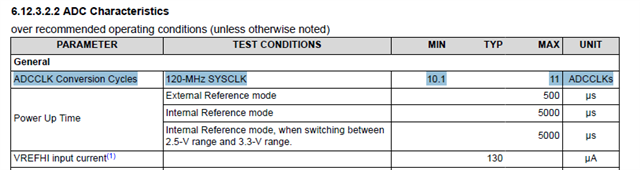

ADC 时钟与 ADC 时序相关。 当 ADC 时钟较小时、转换时间较长、因此对于慢速 ADC、采样率较低。 并从下图中判断、

那么 、当使用 ADCCTL2时。 预分频= 0、 预分频比= 1、ADC 时钟= SYSCLK =120MHz >> 60MHz、ADC 转换时间最小值为11ADCCLKS、对吧?

但我们不知道设置 ADC 频率分频的重要性? 或在应用场景中应用哪种 ADC 频率分频。 您能给我一个示例来帮助理解吗?

由于 ADC 转换时间的影响、ADC 时钟越大、ADC 采样率越高、采样结果和实时性能就越好。 请帮助了解 ADC 时钟的分频设置基础? 非常感谢!