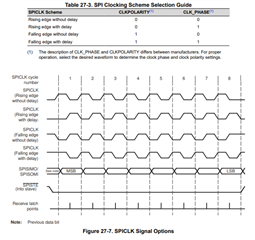

主题中讨论的其他器件:SysConfig

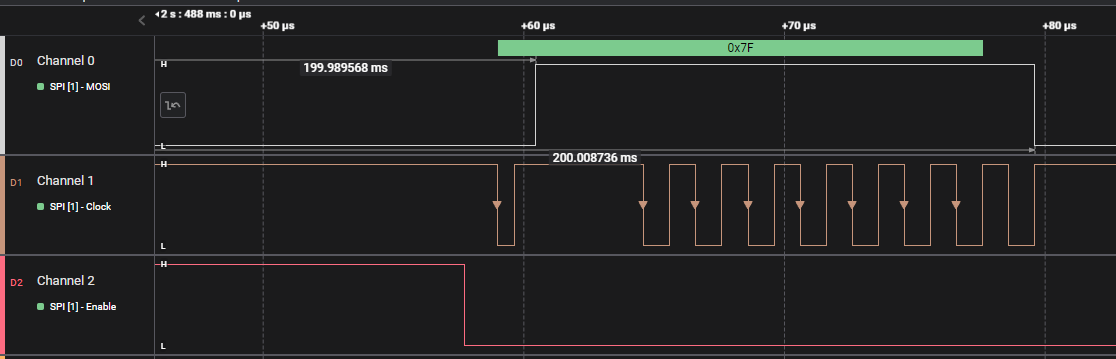

我 使用 SysConfig 在3引脚模式下配置了 SPI。 我选择了用例作为定制、并仅使用了 POCI、PICO 和 CLK 引脚。 不过、当我手动将 CS 引脚设置为低电平、并使用任何 driverlib 函数读取或写入 SPI 数据时、会有一个初始时钟脉冲使数据读取错误。 此脉冲也会出现在4引脚模式下、但在该模式下、CS 引脚仅在初始脉冲结束后才会被拉低。 我如何阻止这种情况发生?

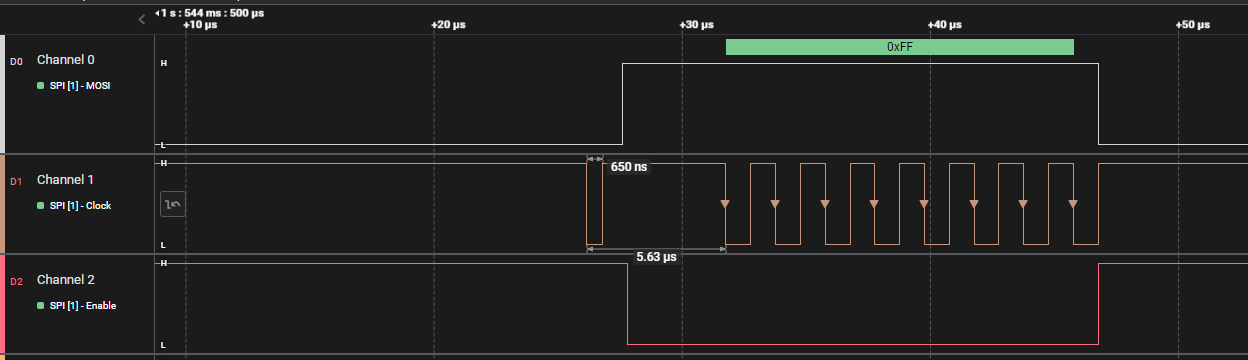

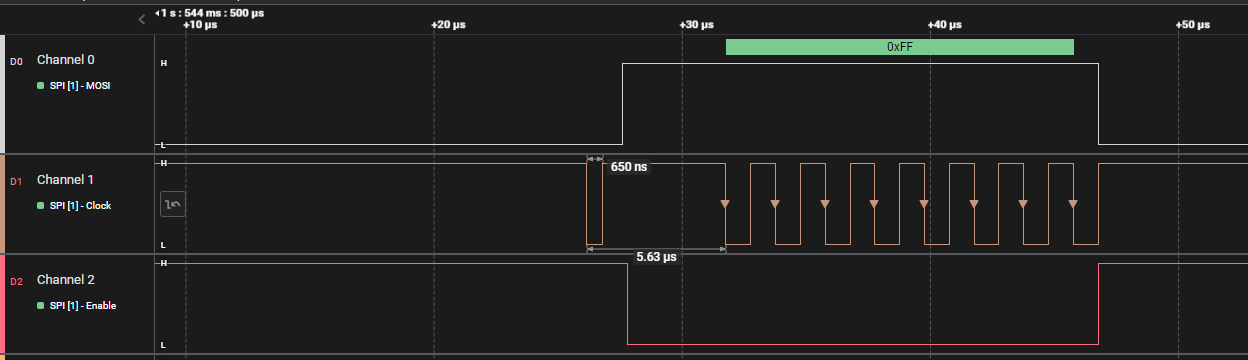

4引脚模式

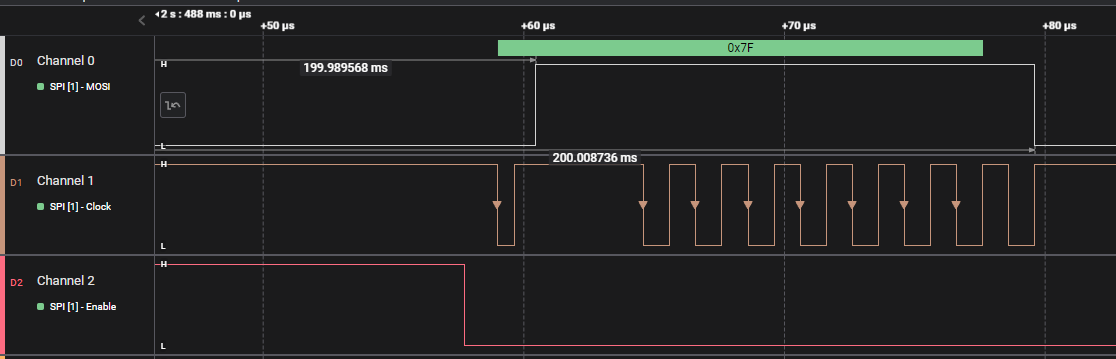

3引脚模式

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我 使用 SysConfig 在3引脚模式下配置了 SPI。 我选择了用例作为定制、并仅使用了 POCI、PICO 和 CLK 引脚。 不过、当我手动将 CS 引脚设置为低电平、并使用任何 driverlib 函数读取或写入 SPI 数据时、会有一个初始时钟脉冲使数据读取错误。 此脉冲也会出现在4引脚模式下、但在该模式下、CS 引脚仅在初始脉冲结束后才会被拉低。 我如何阻止这种情况发生?

4引脚模式

3引脚模式

尊敬的 Gus:

当然、它在这里。

//

// Included Files

//

#include "driverlib.h"

#include "device.h"

#include "board.h"

//#include "f28x_project.h"

//

// Main

//

void main(void)

{

// Device Initialization

Device_init();

//

// Initializes PIE and clears PIE registers. Disables CPU interrupts.

//

Interrupt_initModule();

//

// Initializes the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

Board_init();

//

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

//

EINT;

ERTM;

for(;;)

{

GPIO_writePin(SPI_LTC_CS, 0);

SPI_receiveByte(SPI_LTC_BASE, 0xFF);

SysCtl_delay(0.1*100000000/5);//delay seconds * 100*10E6/5

GPIO_writePin(SPI_LTC_CS, 1);

SysCtl_delay(0.1*100000000/5);

}

}

//

// End of File

//

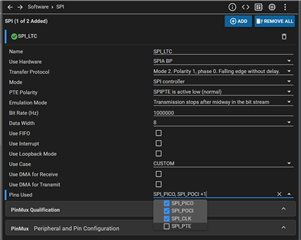

这是3引脚模式下 SPI 外设的 SysConfig 设置。

您可以用以下命令替换代码中的 SPI_receiveByte ()吗? 如果行为有任何不同、请告诉我。

//

// Write to SPI Transmit buffer

//

SPI_writeDataBlockingNonFIFO(SPI_LTC_BASE, 0xFF << (8));

//

// Read SPI Receive buffer

//

rxData = SPI_readDataBlockingNonFIFO(SPI_LTC_BASE);我发现初始时钟脉冲有问题。 在 driverlib 函数 SPI_pollingNonFIFOTransaction ()和 SPI_pollingFIFOTransaction ()中,SPI 模块被禁用并重新启用以设置字符长度。 这 也会被传递到像 spi_receiveByte()这样的宏中,这些宏使用这些函数定义。

是的、这也是我观察到的。 我将把它归档为错误。

但是,逻辑分析仪只能在模式 2中解码数据(CPOL = 1,CPHA = 0)。 但 SPI 外设设置为在模式3下运行。 以下是逻辑分析仪设置为模式3时的轨迹。

SPI 模式不是行业标准。 您会发现不同的供应商对 SPI 模式使用不同的定义。 请参阅 F28002x TRM 中的"SPI"一章、了解基于 CLKPOLARITY 和 CLK_PHASE 设置的预期行为、并相应地配置逻辑分析仪。