您好、专家!

如果同一组的两个中断同时生成、较高优先级的中断将会响应、但低优先级中断标志会被清除吗?

客户遇到以下 情况:

ADCA1和 CIPC0同时生成、并相应地设置 PIEIFRx。 如果 ADC_ISR 响应 CPU//ACK、是否会清除 PIEIFR1.13 (CIPC0)?

或者 确认组并清除组内的任何中断标志?

如果不是、 是否有其他情况会导致 PIEIFR1.13清零? 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、专家!

如果同一组的两个中断同时生成、较高优先级的中断将会响应、但低优先级中断标志会被清除吗?

客户遇到以下 情况:

ADCA1和 CIPC0同时生成、并相应地设置 PIEIFRx。 如果 ADC_ISR 响应 CPU//ACK、是否会清除 PIEIFR1.13 (CIPC0)?

或者 确认组并清除组内的任何中断标志?

如果不是、 是否有其他情况会导致 PIEIFR1.13清零? 谢谢。

您好、绍兴市

感谢您的提问。

[报价 userid="493195" url="~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1279118/tms320f28388d-when-two-interrupt-occurs-on-the-same-group-at-the-same-time ]如果同一组的两个中断同时生成、较高优先级的中断将进行响应、但低优先级中断标志将被清除吗? [/报价]只有在您在中断中自行清除 PIE 中断时、低优先级中断标志才会被清除。 您应该只清除处于其中的 ISR 的 PIE 中断。

Unknown 说:是否会清除 PIEIFR1.13 (CIPC0)?

仅当您清除整个 PIEIFR1时。 只能清除 PIEIEFR1.1

Unknown 说:或 确认组并清除组内的任何中断标志? [/报价]ACK 是独立于 PIEIER 和 PIEIFR 寄存器的。 请参阅下图中来自类似器件 TRM 的图片。 它不会清除该组内的所有 PIEIFR 中断。

如果没有, 是否有其他情况会导致 PIEIFR1.13清除? 谢谢。唯一可以清除 PIEIFR 的是在退出该 ISR 时进行手动清除。

[/quote]

您好、Vince。

双确认、 ACK 不清除组内的所有 PIEIFR 中断。

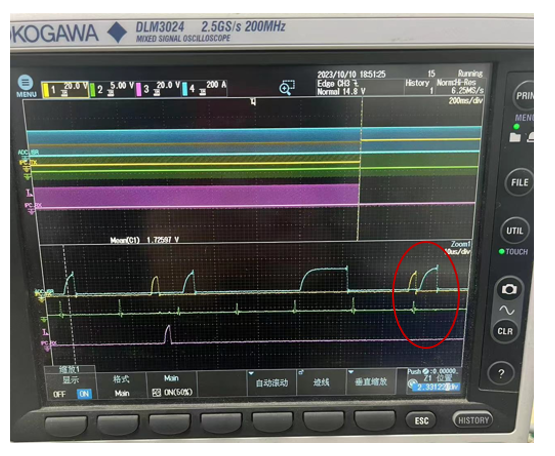

然后 在退出该 ISR 时手动清除 PIEIFR1.1x。 但实际上我们发现我们始终触发 CIPC0中断、但 PIEIFR1.13 不是 自动设置的。 (蓝色:ADC_ISR;黄色:DMA_ISR;紫色:IPC_ISR)。 您可以看到 IPC_ISR 不会正常发生。

那么,PIEIFR1.13将设置哪些条件? PIEIFR1.13哪些条件将被清除?

您好、绍兴市

所以,PIEIFR1.13将设置哪些条件?

唯一专门设置 PIEIFR1.13位的是外设本身。 在这种情况下、CIPC0外设设置 PIEIFR1.13寄存器。

什么条件会被清除? [/报价]在设置后、唯一可以清除它的内容是:

1.手动清除该位的 PIEIFR 寄存器。2.为该中断从 ISR 返回 从中断 x.y 返回的示例清除了 PIEIFRx.y。

因此、除非发生上述两种情况之一、否则不应清除。

是否有机会使用嵌套中断? 如果是、您可能没有意识到 CIPC0中断发生在 ADC 中断内(反之亦然)。

此致、

文斯

您好、Vince。

是的、我们使用 嵌套中断 ADC_ISR 和 DMA_ISR、如下所示:

我们有多个中断、如下设置:

|

中断名称 |

PIE 组和索引 |

优先级 |

备注 |

|

DMA ISR |

7.1 |

1 (最高) |

最高优先级、72kHz 频率 |

|

ADCA ISR |

1.1 |

2 |

将按 DMA ISR、36kHz 频率嵌套 |

|

EPWM1 TZ 中断 |

2.1 |

3 |

在每8个 ADCA ISR 中调用 ProcessA2D_HWI (4.5kHz 频率)。 将按 DMA ISR 和 ADCA ISR 嵌套。 |

|

EPWM1中断 |

3.1 |

4.1 |

软件中断、调用反向零交叉(50 Hz 频率) 将按 DMA ISR 和 ADCA ISR 嵌套。 |

|

EPWM2中断 |

3.2 |

4.2 |

软件中断、调用 UtilityZeroCrossing (50 Hz 频率) 将按 DMA ISR 和 ADCA ISR 嵌套。 |

|

Timer 2中断 |

14 |

0 |

FreeRTOS 节拍定时器 |

此外、如上所述、我们还使用 IPC_ISR。 那么它是否 合理?

您好、绍兴市

并且我们也使用如上所述的 IPC_ISR。

我不确定这句话是什么意思、您能解释一下吗?

无论采用哪种方式、只要 IPC_ISR 发生并返回、都将清除其自身的标志。 这似乎是在这里发生的事情。

此致、

文斯

您好、绍兴市

当同一组中断同时发生时(ADC_ISR 和 IPC_ISR ), 具有较高优先级的 ADC_ISR CPU 将响应,并且具有较低优先级的标志 IPC_ISR 将被保存。 对吗?

是的。 这是事实。 我专门询问您的嵌套的原因是、上表中的 ISR 没有一个提及 IPC_ISR 所完成的操作。

您必须确保允许在其他 ISR 中发生 IPC_ISR。

此致、

文斯

我们将在线程上跟踪该主题。 IPC 专家 Benjamin Collier 将提供帮助。

此致、

文斯

作为对该线程的更新、我们已将该线程与 Vivek Singh 脱机。

我们已经验证、只有当从一个 CPU 向另一个 CPU 发出 IPC 命令、并且中断与组中的另一个中断同时发生时、才会出现该问题。 此时、IPC 标志已就绪、但 IPC 命令似乎未设置 PIE 标志。

我们已经测试过 PIE 上不会发生这种情况、因为我们创建了一个测试来查看同一组中的两个 PIE 中断是否同时(几乎同时发生)复制该问题。

接下来的步骤是 Vivek 计划在本地自行测试此情况、并将与设计一起确定可能导致此问题的原因(可能是同时对 PIE 组进行异步调用等)。

现在关闭该线程、因为调试已离线完成。

此致、

文斯