Other Parts Discussed in Thread: TMDSCNCD28388D

主题中讨论的其他器件:TMDSCNCD28388D

您好!

我一直使用 TMDSCNCD28388D 子板与 SPI 器件通信。 通信设置如下:

-数据宽度: 8位

-比特率: 1Mbps

-模式:控制器

使用上升沿 计时方案(Cpol = 0)时、一切都正常。

然而、 在下降沿方案(Cpol = 1、Cpha = 0或1)上、我看到时钟线上有一个异常行为。

下面是一些波形:

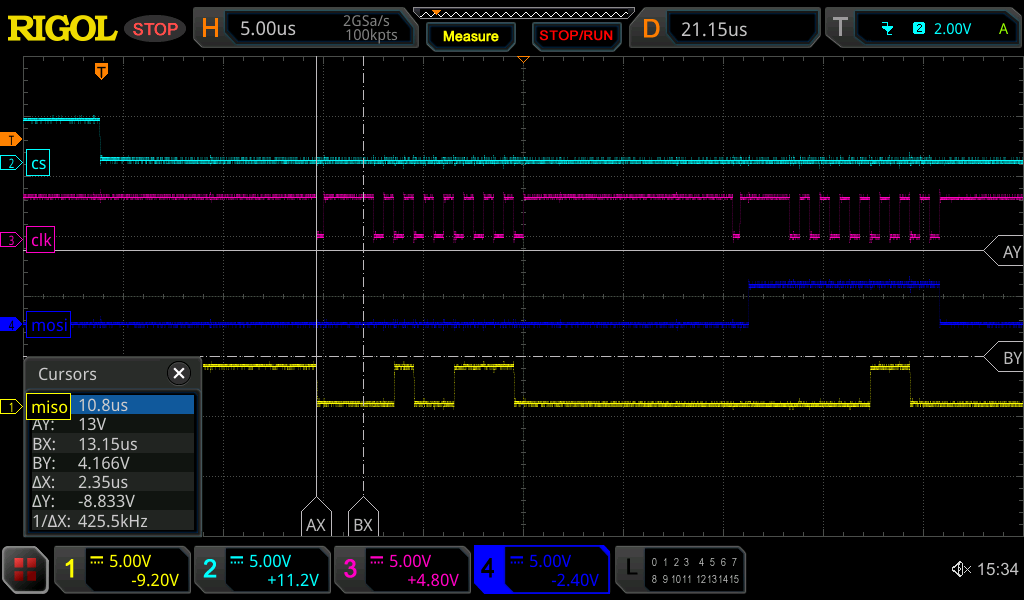

上升沿方案(Cpol = 0)

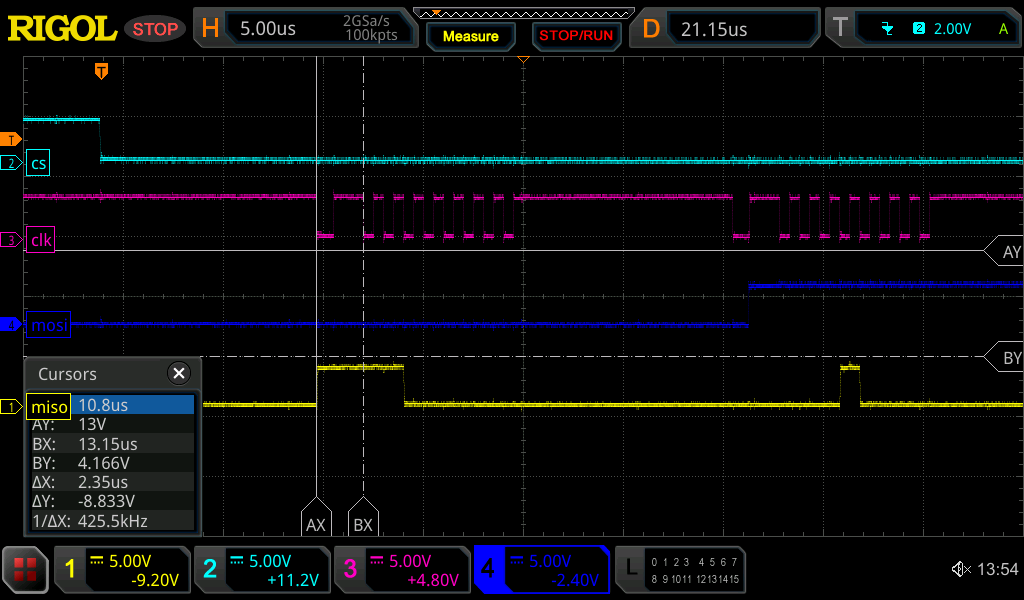

2.下降沿方案(Cpol = 1)

如上面的波形所示、上升沿方案对于8位有确切的8个时钟脉冲。 但是、由于某些原因、下降沿方案有一个额外的脉冲。 由于这个额外的时钟脉冲(看起来像寄生脉冲)、数据(输入/输出)将是错误的。 例如、由于额外脉冲(正常8个脉冲之前和之后)、MOSI 数据应该为0xFF、但锁存为0x3F。

我 尝试了所有 SPI 模块(SPIA、B、C、D)、并使用了不同的时钟引脚、但仍然面临同样的问题。

我的配置代码与 spi_ex6_eeprom 示例工程类似(只是 我使用的是 SPI_PROT_POL1PHA0或 SPI_PROT_POL0PHA1 )。

void mySPI0_init (){

SPI_disableModule (mySPI0_BASE);

SPI_setConfig (mySPI0_BASE、DEVICE_LSPCLK_FREQ、SPI_PROT_POL1PHA0、

SPI_MODE_CONTROL、1000000、8);

SPI_setPTESignalPolarity (mySPI0_BASE、SPI_PTE_ACTIVE_LOW);

SPI_disableFIFO (mySPI0_BASE);

SPI_disableLoopback (mySPI0_BASE);

SPI_setEmulationMode (mySPI0_BASE、SPI_emulation_stop_midway);

SPI_enableModule (mySPI0_BASE);

}

void PinMux_init ()

{

GPIO_setPinConfig (GPIO_11_GPIO11);

GPIO_setPinConfig (mySPI0_SPIPICO_PIN_CONFIG);

GPIO_setPadConfig (mySPI0_SPIPICO_GPIO、GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode (mySPI0_SPIPICO_GPIO、GPIO_QUAL_ASYNC);

GPIO_setPinConfig (mySPI0_SPIPOCI_PIN_CONFIG);

GPIO_setPadConfig (mySPI0_SPIPOCI_GPIO、GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode (mySPI0_SPIPOCI_GPIO、GPIO_QUAL_ASYNC);

GPIO_setPinConfig (mySPI0_SPICLK_PIN_CONFIG);

GPIO_setPadConfig (mySPI0_SPICLK_GPIO、GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode (mySPI0_SPICLK_GPIO、GPIO_QUAL_ASYNC);

}

请告诉我、如果我 错过了任何内容 、以便时钟在 下降沿方案中正常工作。

非常感谢、

此致、