主题中讨论的其他器件:C2000WARE、 UNIFLASH

工具与软件:

您好!

我在 F28003x Launchpad 中成功使用了 DCAN 闪存内核、并在闪存引导模式下通过在闪存组中刷写内核来使用 CAN 更新固件。 现在、我要将该内核移植到 F28002x Launchpad。 我怎么能做到这一点?

谢谢!

Hariprasath

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我在 F28003x Launchpad 中成功使用了 DCAN 闪存内核、并在闪存引导模式下通过在闪存组中刷写内核来使用 CAN 更新固件。 现在、我要将该内核移植到 F28002x Launchpad。 我怎么能做到这一点?

谢谢!

Hariprasath

嗨、Hari、

以下是为该器件生成 DCAN 闪存内核所需的操作列表:

首先、您可以 遵循 C2000ware Resource Explorer 中的迁移指南生成器:

嗨、Hari、

根据您对 FsmStatus 的屏幕截图、闪存内核可能正在尝试对尚未擦除的闪存位置重新编程。 请参阅 闪存 API 指南的表8 、了解 FMSTAT 的每个位代表什么。

此外、根据您发送的链接器文件、看起来您正在尝试在闪存中加载和运行闪存内核。 默认情况下、闪存内核示例从 RAM 执行。 如果您想将闪存内核保留在闪存中、这没问题、但您必须从 RAM 运行所有闪存 API 函数(以及调用闪存 API 的函数)。 链接器 cmd 文件的.TI.ramfunc 段应具有基于闪存的加载地址和基于 RAM 的运行地址。 有关示例、请参阅 C2000Ware 中的28002x_generic_flash_lnk.cmd (C2000Ware_5_02_00_00\device_support\f28002x\common\cmd)

此致、

Skyler

您好、Skyler:

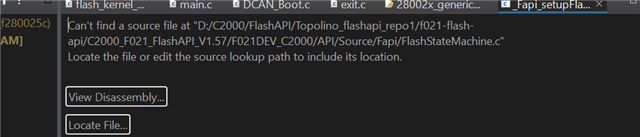

IAM 尝试使用 28002x_GENERIC_FLASH_lnk.cmd 时 、我的程序卡在"No source available for SYSCTL_DELAY ()"中

随附了参考的屏幕截图。

MEMORY

{

RAMM0 : origin = 0x000128, length = 0x0002D8

RAMM1 : origin = 0x000400, length = 0x0003F8

RAMLS456 : origin = 0x0000A000, length = 0x00001800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x0007F8

FLASH_BANK0_SEC0 : origin = 0x080000, length = 0x001000

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x000FF0

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > 0x080000,ALIGN(8)

.text : >> FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3 | FLASH_BANK0_SEC4, ALIGN(8)

.cinit : > FLASH_BANK0_SEC1, ALIGN(8)

.switch : > FLASH_BANK0_SEC1, ALIGN(8)

.reset : > RESET, TYPE = DSECT

.binit : > FLASH_BANK0_SEC1, ALIGN(8)

.ovly : > FLASH_BANK0_SEC1, ALIGN(8)

.stack : > RAMM0

.init_array : > FLASH_BANK0_SEC1, ALIGN(8)

.bss : > RAMLS456

.bss:output : > RAMLS456

.bss:cio : > RAMGS0

.const : > FLASH_BANK0_SEC4, ALIGN(8)

.data : > RAMLS456

.sysmem : > RAMLS456

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMGS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

谢谢!

haripasath。

您好、Skyler:

现在、当 IAM 调用设置活动闪存功能运行出程序时、该问题被清除。

已附上该屏幕截图供您参考。

初始化成功但活动的闪存组失败、这可能是什么问题?

为参考附加了 cmd 文件

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS4 : origin = 0x0000A000, length = 0x00000800

// RAMLS5 : origin = 0x0000A800, length = 0x00000800

// RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800

/* Combining all the LS RAMs */

RAMLS56 : origin = 0x0000A800, length = 0x00001000

RAMGS0 : origin = 0x0000C000, length = 0x000007F8

// RAMGS0_RSVD : origin = 0x0000C7F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

// FLASHBANK1 : origin = 0x00080000, length = 0x0000FFF0

// FLASH_BANK1_RSVD : origin = 0x0008FFF0, length = 0x00000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

BOOTROM : origin = 0x003F0000, length = 0x00008000

BOOTROM_EXT : origin = 0x003F8000, length = 0x00007FC0

RESET : origin = 0x003FFFC0, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE /* on-chip Flash */

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x000FF0 /* on-chip Flash */

// FLASH_BANK0_SEC15_RSVD : origin = 0x08FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3 | FLASH_BANK0_SEC4, ALIGN(8)

.cinit : > FLASH_BANK0_SEC1, ALIGN(8)

.switch : > FLASH_BANK0_SEC1, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

.init_array : > FLASH_BANK0_SEC1, ALIGN(8)

.bss : > RAMLS4

.bss:output : > RAMLS4

.bss:cio : > RAMGS0

.const : > FLASH_BANK0_SEC1, ALIGN(8)

.data : > RAMLS4

.sysmem : > RAMLS4

ramgs0 : > RAMGS0

/* Allocate IQ math areas: */

IQmath : > RAMLS4

IQmathTables : > RAMLS4

.TI.ramfunc LOAD = FLASH_BANK0_SEC1,

RUN = RAMGS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

谢谢!

Hari

Hari、

感谢您进行更正(之前与 F28003x 器件接头进行比较)。

调用时、Fapi_setActiveFlashBank 函数是否驻留在 RAM 中? 为此、 您可以检查生成的 .map 文件以了解放置此函数的地址?

另一个要尝试的是 RAM LS4567区域、以容纳闪存 API 并将.TI.ramfunc 的函数组合在一起。 对于 F28002x 器件、您可以参考 flashapi_ex1_programming 工程的28002x_flash_api_lnk.cmd 文件。

谢谢!

Charles

尊敬的 Charles:

我注意到其他情况、而 IAM 使用缓冲区大小8、我可以向闪存中写入除起始扇区地址之外的所有内容。 [已使用 unifialsh 来验证闪存]

从文本到康铜的和写。

这是我的应用程序的链接器 cmd 文件。

MEMORY

{

RAMM0 : origin = 0x000128, length = 0x0002D8

RAMM1 : origin = 0x000400, length = 0x0003F8

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x0007F8

FLASH_BANK0_SEC0 : origin = 0x080000, length = 0x001000

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x000FF0

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

//

// C28x Sections

//

.reset : > RESET, TYPE = DSECT /* not used, */

codestart : > 0x084000, ALIGN(8)

.text : >> FLASH_BANK0_SEC6 | FLASH_BANK0_SEC7 | FLASH_BANK0_SEC8,

ALIGN(8)

.TI.ramfunc : > FLASH_BANK0_SEC5,

ALIGN(8)

.binit : > FLASH_BANK0_SEC5,

ALIGN(8)

.ovly : > FLASH_BANK0_SEC5,

ALIGN(8)

.cinit : > FLASH_BANK0_SEC5,

ALIGN(8)

.stack : > RAMM0

.init_array : > FLASH_BANK0_SEC5,

ALIGN(8)

.bss : > RAMLS7

.const : > FLASH_BANK0_SEC8,

ALIGN(8)

.data : > RAMLS7

.switch : > FLASH_BANK0_SEC8,

ALIGN(8)

.sysmem : > RAMLS7

}

内核链接器文件

-stack 0x380

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* RAMLS4 : origin = 0x0000A000, length = 0x00000800

RAMLS5 : origin = 0x0000A800, length = 0x00000800

RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800*/

/* Combining all the LS RAMs */

RAMLS4567 : origin = 0x0000A000, length = 0x00002000

RAMGS0 : origin = 0x0000C000, length = 0x000007F8

// RAMGS0_RSVD : origin = 0x0000C7F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

BOOTROM : origin = 0x003F0000, length = 0x00008000

BOOTROM_EXT : origin = 0x003F8000, length = 0x00007FC0

RESET : origin = 0x003FFFC0, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE /* on-chip Flash */

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x000FF0 /* on-chip Flash */

// FLASH_BANK0_SEC15_RSVD : origin = 0x08FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3 , ALIGN(8)

.cinit : > FLASH_BANK0_SEC1, ALIGN(8)

.switch : > FLASH_BANK0_SEC1, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

.init_array : > FLASH_BANK0_SEC1, ALIGN(8)

.bss : > RAMLS4567

.bss:output : > RAMLS4567

.bss:cio : > RAMGS0

.const : > FLASH_BANK0_SEC1, ALIGN(8)

.data : > RAMLS4567

.sysmem : > RAMLS4567

ramgs0 : > RAMGS0

GROUP

{

.TI.ramfunc

{ -l FlashAPI_F28002x_FPU32.lib}

}LOAD = FLASH_BANK0_SEC1,

RUN = RAMLS4567,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

DataBufferSection : > RAMGS0, ALIGN(8)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

/*

//===========================================================================

// End of file.

//===========================================================================

*/

谢谢!

Hariprasath

您好!

0x8C000处写入的是什么? 根据链接器文件、存储体0扇区12中未存储任何内容(从0x8C000开始)。

并且我注意到其他一些东西而 IAM 使用缓冲区大小8我可以写入闪存中除起始扇区地址之外的所有内容。

0x8C000是您在这里指的扇区起始地址吗?

此致、

Skyler

您好、Skyler:

现在我可以使用内部振荡器、在我使用 Blinkey 应用程序时、其工作原理就像。

但是、当我使用电机控制工程时、它在 ISR1 ram 函数[ program error & correct_data_buffer_length]中发生故障

附加了链接器 cmd 文件用于参考

MEMORY

{

RAMM0S : origin = 0x000128, length = 0x000158

RAMM1D : origin = 0x000280, length = 0x000578

RAMLS4 : origin = 0x00A000, length = 0x000600

RAMLS567 : origin = 0x00A600, length = 0x001A00

RAMGS0 : origin = 0x00C000, length = 0x0007F8

FLASHBANK0_BOOT : origin = 0x083002, length = 0x000FFE

FLASHBANK0_CODE : origin = 0x084002, length = 0x009FFE

FLASHBANK0_DATA : origin = 0x08E000, length = 0x001000

FLASHBANK0_PRMS : origin = 0x08F000, length = 0x000FF0

RESET : origin = 0x3FFFC0, length = 0x000002

BEGIN : origin = 0x083000, length = 0x000002

}

SECTIONS

{

.reset : > RESET, TYPE = DSECT

codestart : > BEGIN, ALIGN(8)

controlVariables : > RAMLS567

.text : > FLASHBANK0_CODE, ALIGN(8)

GROUP

{

.TI.ramfunc

ramfuncs

isrcodefuncs

/* Digital Controller Library functions */

dclfuncs

dcl32funcs

} LOAD = FLASHBANK0_CODE

RUN = RAMLS567,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

ctrlfuncs : LOAD = FLASHBANK0_CODE

RUN = RAMLS567,

LOAD_START(ctrlfuncsLoadStart),

LOAD_SIZE(ctrlfuncsLoadSize),

LOAD_END(ctrlfuncsLoadEnd),

RUN_START(ctrlfuncsRunStart),

RUN_SIZE(ctrlfuncsRunSize),

RUN_END(ctrlfuncsRunEnd),

ALIGN(8)

.binit : > FLASHBANK0_DATA, ALIGN(8)

.cinit : > FLASHBANK0_DATA, ALIGN(8)

.stack : > RAMM0S

.init_array : > FLASHBANK0_CODE, ALIGN(8)

.bss : > RAMM1D

.const : > FLASHBANK0_CODE, ALIGN(8)

.data : > RAMM1D

.switch : > FLASHBANK0_CODE, ALIGN(8)

.sysmem : > RAMM1D

est_data : > RAMLS4

/* Allocate IQ math areas: */

IQmath : > RAMLS567

IQmathTables : > RAMLS567

FPUmathTables : > FLASHBANK0_DATA, ALIGN(8)

}

SECTIONS

{

prms_data : > FLASHBANK0_DATA, ALIGN(8)

GROUP

{

user_data

foc_data

}

LOAD = RAMM1D

LOAD_START(ctrlVarsLoadStart),

LOAD_SIZE(ctrlVarsLoadSize),

LOAD_END(ctrlVarsLoadEnd)

GROUP

{

sys_data

ctrl_data

motor_data

}

LOAD = RAMGS0

LOAD_START(motorVarsLoadStart),

LOAD_SIZE(motorVarsLoadSize),

LOAD_END(motorVarsLoadEnd)

GROUP

{

vibc_data

dmaBuf_data

datalog_data

graph_data

sfra_data

SFRA_F32_Data

}

LOAD = RAMGS0

LOAD_START(extVarsLoadStart),

LOAD_SIZE(extVarsLoadSize),

LOAD_END(extVarsLoadEnd)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

Thnaks,

Hariprasath。