工具与软件:

您好!

根据数据表("数据表 F28P55x")、其中指出每个样本的转换时间可以为180ns。

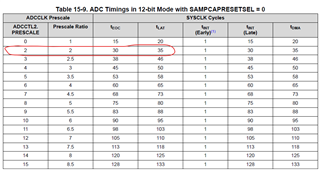

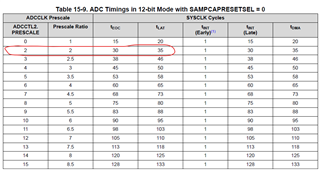

但是、如果您查看用户手册中的 ADC 规格、我认为对于 F28P550SJ (150MHz 系统时钟速率)、ADC 外设时钟的速度只能达到75MHz 的速度。 这意味着我们需要设置预分频= 2、这会导致转换时间超过180ns。

您能否向我解释一下为何数据表中使用了180ns 转换时间?

谢谢!

Frank

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

根据数据表("数据表 F28P55x")、其中指出每个样本的转换时间可以为180ns。

但是、如果您查看用户手册中的 ADC 规格、我认为对于 F28P550SJ (150MHz 系统时钟速率)、ADC 外设时钟的速度只能达到75MHz 的速度。 这意味着我们需要设置预分频= 2、这会导致转换时间超过180ns。

您能否向我解释一下为何数据表中使用了180ns 转换时间?

谢谢!

Frank

尊敬的 Susmitha:

感谢您的答复、但它没有回答我的问题。

我知道 ADC 转换时间为 tsh + tlat。 让我们为 tsh 使用1个时钟周期、这是非常极端的、并且如前所述、预分频的最小值为2、使得外设时钟为75MHz、相关的 tlat 为35个外设时钟周期。

因此、ADC 转换的总时钟周期为 tsh + tlat = 1 + 35 = 36。

假设时钟速率为75MHz、每个时钟周期为13、3ns、总 ADC 转换时间为36 * 13.3ns = 478.8ns。 这比数据表中规定的180ns 大得多。

我的问题是、180ns 是如何得出的? 我在计算中遗漏了什么?

谢谢!

Frank