Other Parts Discussed in Thread: TPS562201

主题中讨论的其他器件:TPS562201

工具与软件:

2.2 压摆率问题:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TPS562201

工具与软件:

Angela、

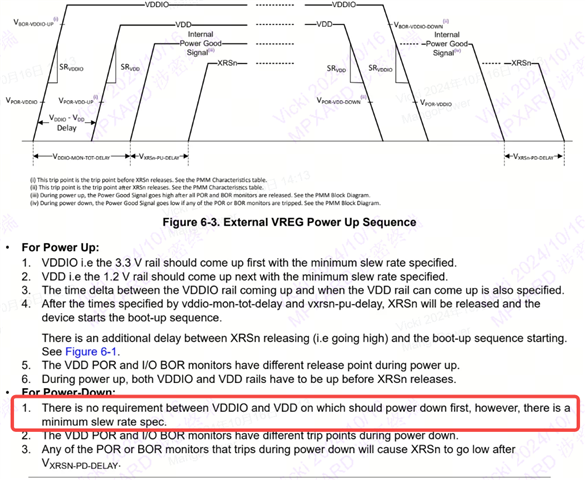

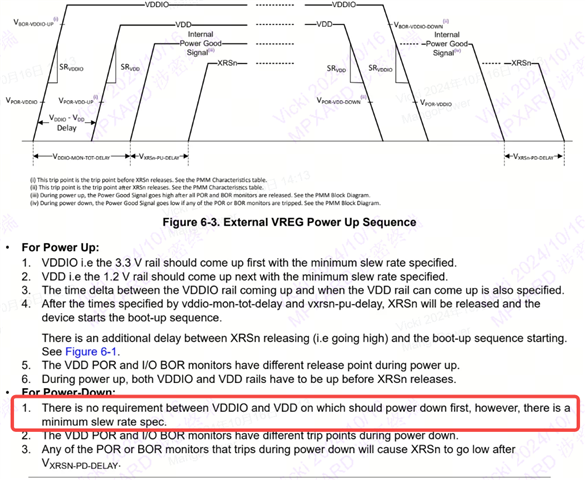

请参阅数据表的这一部分、了解上述部分所需的一些背景信息:

此处假设 VDD 由外部监控、因此对于外部 VDD 电源情况、VDD 的好坏不成问题。

因此、2.1没有要求、并假设 VDD 正在受到监测。 否则、内部 VDD POR 跳闸点太低、在触发 XRSn 并将其驱动为低电平之前无法保证器件的正常运行

对于2.2:

上电风险在于、如果上升时间太慢、BOR 可能会在电压稳定在正确区域之前释放。 客户可以参考时序延迟以及 BOR 发布范围、以确定是否存在风险

对于断电、我认为同样的速度太慢的风险、但由于 BOR 完全正常工作、因此它的风险应该比上电低。

在这两种情况下、我认为如果斜坡过快、则存在激活器件中的 ESD 二极管并消耗过多电流和/或锁存 IO 缓冲器的风险。

对于 VDD 的斜升速率、由于我们再次假设该电源轨上有外部监控器、因此更像是器件看到的受控上电。

此致!

Matthew

DANG、

感谢新的信息,这有助于很多。

我认为 VDD 延迟在这方面有所帮助、可避免 VDDIO 线路上升时间较长的问题。

由于 VDD 在~2.85V 之前根本不接通、它也在 原本可能是一个不决定因素的时间内保持 XRSn。 当它出现时、VDDIO 已经在正常范围内、这样内部 BOR 监控器此时也处于稳定/已知正常状态。

还可以看到、在 DS 中的预期范围之前、XRSn 系列没有释放、这也表明内部没有实现稳定。

如果我们认为这种 VDDIO/VDDIO 关系 VDD 可以保持 I 正常、从而违反最小压摆率、则器件将完全退出复位状态并正确运行。

有一点很好奇、在 VDDIO 几乎完成斜坡之前、VDD 的关闭源是什么?

此致!

Matthew

DANG、

我来提供更多详细信息。

DS 中列出的上升时间主要是为了确保内部 POR/BOR 监控电路使器件保持复位状态、直到电源处于规格范围内。

当 VREGENz = 0V (不是您的用例)时、内部 VREG 为1.2V 内核电源供电 、而该电源的优缺点是 POR/BOR 释放复位的初级栅极。 反过来、该电源的斜升速率也是我们关心的所有问题。

但是、当 VREGENz= VDDIO (您的用例)时、也会从外部为1.2V 供电、这也会释放复位。

如您所述、来自降压转换器的 VDDIO 斜坡太慢/长于我们为 VDDIO 提供的 DS 规格。 通常、这会带来一个问题、即内部 POR/BOR 将在 VDDIO 在范围内之前过早释放、并且可能存在器件过早开始执行代码的风险。

但是、根据波形、VDD (1.2V)直到 VDDIO (3.3V)达到或接近2.60V 时才会激活、这会降低 VDDIO 上的慢速斜升速率、从而正确地保持复位取消置位。 当 VDD 电源轨变为高电平时、精确的 VDDIO 监控器就会在规格范围内工作、并且我们能够正确地门控复位。

因此、即使我们违反了 VDDIO 上的最小斜坡速率、但由于应用 VDD 的方式、我可以放弃该要求、因为在系统级别、我们要避免 VDDIO 上缓慢斜坡可能导致的条件。

基本上、我认为您的电流实施将在上电后正确运行、因此您可以忽略 VDDIO 上的缓慢斜坡/违反 DS。

此致!

Matthew

DANG、

2.45V 不在 DS 中、通过指定 VDDIO/XRSn 的斜坡速率以及内部 POR/BOR 的构建方式、我们将确保在释放 VDD 之前准确监控 VDDIO 电源轨。

不过、在您的情况下、由于 VDD 保持低电平并且不会随 VDDIO 上升、因此我们不必如此严格地限制斜升速率、因为 VDD 为0V 也可以保证 XRSn 保持不变、即使 VDDIO 在规格范围内也是如此。

这不是我们预期的情况、因此我们只给出了斜坡速率与器件内部不同监视器的所有不同开启/工作条件的对比。

斜升速率、连同我之前提到的方框图中的延迟、将确保 POR/BOR 不会过早地释放复位。

此致!

Matthew

@MatthewRate ???