Thread 中讨论的其他器件: C2000WARE

工具与软件:

您好!

我目前正在将一个项目从 LAUNCHXL-F280049迁移到 LAUNCHXL-F280039C。

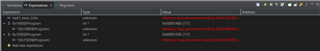

目前、我成功地在新的 Launchpad 中进行了编译、链接和运行、但是我注意到 DATA_SECITONS Cla1ToCpuMsgRAM 和 CpuToCla1MsgRAM 的所有变量部分在表达式视图中都不可见。

例如、在上面一个名为 task1_exec_tick 的变量位于 Cla1ToCpuMsgRAM 上、但除非我连接和调试 CLA、否则不可见、这与我在之前的 DSP (F280049)上使用的变量不同。

您也可以在前一个图像中检查的内容中、我无法在这些存储器扇区 CLA1_MSGRAMLOW 或 CLA1_MSGRAMHIGH 上看到变量 。 因此这让我相信 内存中的特定区域发生了某种事情。

#define _BOOTLOADER_ON_

MEMORY

{

#ifdef _BOOTLOADER_ON_

FLASH_APP_VALID_E : origin = 0x00080000, length = 0x000001, fill=0x0110 /* on-chip Flash App ; APP_VALID 0x0110*/

SWVERSIONSEC : origin = 0x00080001, length = 0x000100, fill=0xFFFF

ADDR_VERSIONINFO : origin = 0x00080101, length = 0x000006, fill=0xFFFF

RESEVED : origin = 0x00080107, length = 0x000003, fill=0xFFFF

BEGIN : origin = 0x00080200, length = 0x000002

#else

BEGIN : origin = 0x00080200, length = 0x00000002

#endif

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS0 : origin = 0x00008000, length = 0x00000800

RAMLS1 : origin = 0x00008800, length = 0x00000800

RAMLS2_TO_LS7 : origin = 0x00009000, length = 0x00002800 // And using 0x100 more available

RAMGS0 : origin = 0x0000C000, length = 0x00001000

RAMGS1 : origin = 0x0000D000, length = 0x00001000

RAMGS2 : origin = 0x0000E000, length = 0x00001000

RAMGS3 : origin = 0x0000F000, length = 0x00000FF8

// RAMGS3_RSVD : origin = 0x0000FFF8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

BOOTROM : origin = 0x003F8000, length = 0x00007FC0

SECURE_ROM : origin = 0x003F2000, length = 0x00006000

RESET : origin = 0x003FFFC0, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK_RESERVED : origin = 0x080202, length = 0x000DFE

FLASH_BANK_INIT : origin = 0x081000, length = 0x001000

FLASH_BANK_CPU : origin = 0x082000, length = 0x00D000

FLASH_BANK0_CPU_CONST : origin = 0x08F000, length = 0x001000

/* BANK 1 */

FLASH_BANK_CLA : origin = 0x090000, length = 0x010000

/* BANK 2 */

FLASH_BANK2 : origin = 0x0A0000, length = 0x010000

// FLASH_BANK0_CPU_CONST_RSVD : origin = 0x0AFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

}

SECTIONS

{

codestart : > BEGIN, ALIGN(4)

.text : >> FLASH_BANK_CPU, ALIGN(4)

.cinit : > FLASH_BANK_INIT, ALIGN(4)

.switch : > FLASH_BANK_INIT, ALIGN(4)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

#ifdef _BOOTLOADER_ON_

swversionsec : > SWVERSIONSEC

.Versioninfo : > ADDR_VERSIONINFO

#endif

#if defined(__TI_EABI__)

.init_array : > FLASH_BANK_INIT, ALIGN(4)

.bss : > RAMLS0

.bss:output : > RAMLS0

.bss:cio : > RAMLS0

.data : > RAMLS0

.sysmem : > RAMLS0

.const : > FLASH_BANK0_CPU_CONST ALIGN(4)

#else

.pinit : > FLASH_BANK_INIT ALIGN(4)

.ebss : >>RAMGS0

.esysmem : > RAMGS0

.cio : > RAMLS0

.econst : > FLASH_BANK0_CPU_CONST

#endif

ramgs0 : > RAMGS0

ramgs1 : > RAMGS1

//----------------------------------------------------------------------------------------------------------------

ramconsts : LOAD >> FLASH_BANK0_CPU_CONST

RUN = RAMLS0

IQmath : > FLASH_BANK0_CPU_CONST, ALIGN(4)

IQmathTables : > FLASH_BANK0_CPU_CONST, ALIGN(4)

FPUmathTables : > FLASH_BANK0_CPU_CONST, TYPE = NOLOAD

#if defined(__TI_EABI__)

.TI.ramfunc : LOAD = FLASH_BANK0_CPU_CONST,//FLASH_BANK0_SEC1

RUN = RAMGS2 | RAMGS3,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : LOAD = FLASH_BANK0_CPU_CONST,

RUN = RAMGS2 | RAMGS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

#if defined(__TI_EABI__)

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK_CLA,

RUN = RAMLS2_TO_LS7,

LOAD_START(Cla1ProgLoadStart),

RUN_START(Cla1ProgRunStart),

LOAD_SIZE(Cla1ProgLoadSize),

ALIGN(8)

#else

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK_CLA,

RUN = RAMLS2_TO_LS7,

LOAD_START(_Cla1ProgLoadStart),

RUN_START(_Cla1ProgRunStart),

LOAD_SIZE(_Cla1ProgLoadSize),

ALIGN(8)

#endif

.scratchpad : > RAMLS1

.bss_cla : > RAMLS1

Cla1DataRam : > RAMLS1

cla_shared : > RAMLS1

CLADataLS1 : > RAMLS1

#if defined(__TI_EABI__)

.const_cla : LOAD = FLASH_BANK_CLA,

RUN = RAMLS2_TO_LS7,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize),

ALIGN(8)

#else

.const_cla : LOAD = FLASH_BANK_CLA,

RUN = RAMLS2_TO_LS7,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize),

ALIGN(8)

#endif

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH

}

我一直在阅读一些帖子、甚至检查了 ccs1270文件夹 C:\ti\ccs1270\ccs\ccs_base\emulation\gel\f280039.gel 中的 GEL 文件。 如果加载 Memory Map 视图、则可以看到该存储器部分可读且可写入:

到目前为止、所有内容都可能表明我的问题在于这些内存区域的可视化。 这是因为即使 CCS 看不到这些变量、如果我进行分步调试、我也可以看到 CPU1读取的值与 CLA1写入的值相同。

几天后,我自己想寻找更多的想法来解决这个问题。

所以我愿意接受任何建议