工具与软件:

尊敬的 TI:

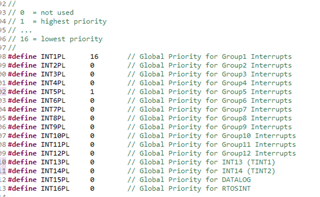

在我的应用程序中、我使用 Timer0中断和 CLB1中断、我的应用程序要求 CLB1中断的优先级高于 Timer0中断、并且在 Timer0 ISR 期间提供 CAN 中断。 我以 interrupt_ex3_sw_Prioritization 的示例为例、并经过 https://software-dl.ti.com/C2000/docs/c28x_interrupt_nesting/html/index.html 、但到目前为止它不起作用。 您能否建议如何配置以使 CLB1中断被嵌套并具有更高的优先级到 Timer0中断?

非常感谢。

我的无法正常工作的代码如下所示:

// Timer0 ISR - Lowwer priority

interrupt void INT_myCPUTIMER0_ISR(void)

{

//

// Save IER register on stack

//

volatile uint16_t tempPIEIER = HWREGH(PIECTRL_BASE + PIE_O_IER1);

//

// Set the global and group priority to allow CPU interrupts

// with higher priority

//

IER |= M_INT5;

// IER |= M_INT1;

IER &= MINT5;

// IER &= MINT1;

// HWREGH(PIECTRL_BASE + PIE_O_IER1) &= MG1_7;

// HWREGH(PIECTRL_BASE + PIE_O_IER1) &= MG5_5;

// HWREGH(PIECTRL_BASE + PIE_O_IER5) &= MG5_5;

//

// Enable Interrupts

//

Interrupt_clearACKGroup(0xFFFFU);

__asm(" NOP");

EINT;

// Execute ISR task

// My code is here

//

// Disable interrupts and restore registers saved:

//

DINT;

HWREGH(PIECTRL_BASE + PIE_O_IER1) = tempPIEIER;

}

__interrupt void INT_CLB1_ISR(void)

{

//

// Set the global priority to allow CPU interrupts with higher priority

//

IER &= MINT5;

EINT;

// CLB ISR task

// My code is here

CLB_clearInterruptTag(CLB1_BASE);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP5);

//

// Disable Interrupts

//

DINT;

}