工具与软件:

嗨、团队:

在相关主题上、我们有一些关于部件上电的问题。

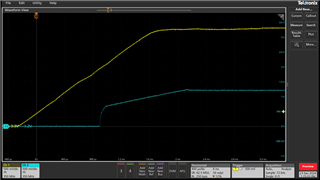

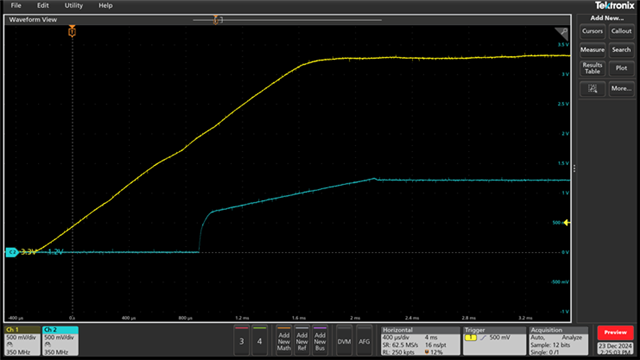

在设计中、VDD 为1.2V。 VDDOSC/VDDIO/VDD3V3FL 连接到3.3V。

其中一项设计在 VDDOSC/VDDIO/VDD3V3FL 之后将 VDD 斜坡(1.2V)的启动延迟了1毫秒、并具有较高的启动斜升速率。

否则、VDD 和 VDDOSC/VDDIO/VDD3V3FL 始终处于通电/断电状态。

请查看下面的图片。

在这种情况下:

上电时、当 VDD 关闭1ms 时、VDDOSC 将通电。

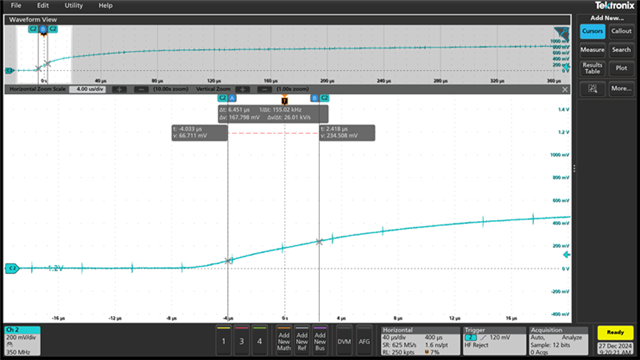

在低于2000v/s 的稳定状态下、前10us 内 VDD 的初始斜升速率为26kv/s

这是否满足要求:

"必须同时打开和关闭 VDDOSC 和 VDD。 当 VDD 关闭时、VDDOSC 不能通电。"

电源斜升速率介于330和10^5V/s 之间

感谢您的支持、

Luke