工具与软件:

您好、工程师

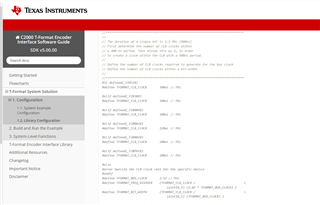

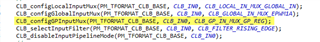

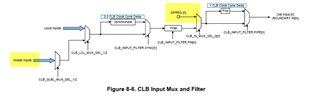

现在我打算使用 CLB 来实现 T-format 协议、请查看28p55的数据表 c2000、Ware_Motor t5213Format_f28p65x_comms_demo、它们很难理解和直接使用。

以下链接中的文档也是无效的、我想得到一些帮助。

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1007238/faq-configurable-logic-block-clb---how-do-i-get-started

还有另外两个问题:

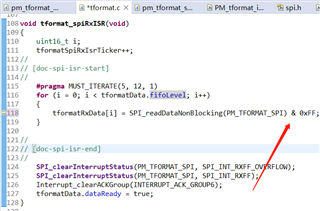

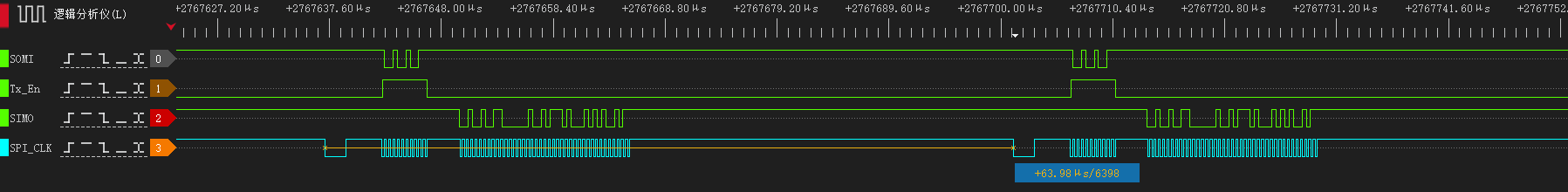

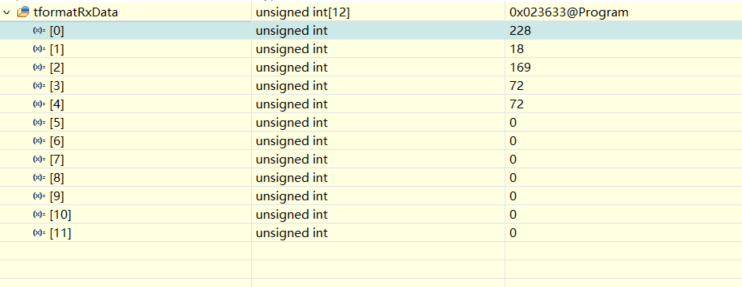

1.在 tformat_f28p65x_comms_demo 例程中、CLB 是否仅控制 RS485的方向? 接收到编码器返回的数据后、它是否首先输入到 CLB、然后是 CLB 确定到下降沿的 CLK、然后输出 SPI?

2.没有28p55的 CLB 库在 C2000 Ware_Motor 中, 28p65的 CLB 库是28p55?