主题中讨论的其他器件: LMK5B12204

工具/软件:

您好、

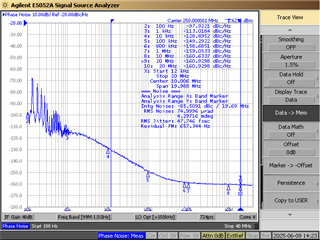

我需要一个 250MHz 时钟来馈送 ADC。 我的抖动目标< 70fs。

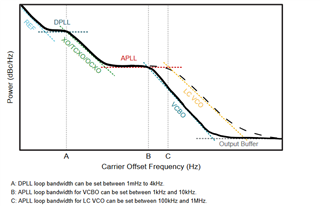

数据表中报告的性能(仅在 DPLL 模式和 APPL1 下)似乎符合我的要求。

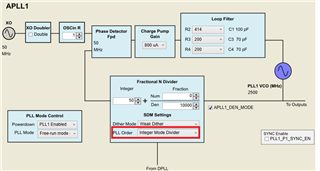

- 是否可以仅使用 APLL1 并关闭 DPLL 来实现小于 70fs 的抖动?

- 不使用 DPLL 的缺点是什么?

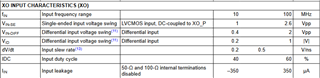

- 在 DPLL 关闭的情况下、我是否可以使用 50 或 100MHz XO? (APLL1 的输入和输出频率之间的比率将为整数。)

- 如果我使用 DPLL 但没有基准 (PRIREF 或 SECREF)、会发生什么情况? 这是允许的配置吗?

- 我是否可以将来自 FPGA 的 25MHz 时钟用作 DPLL 的 PRIREF?

谢谢

此致

Alberto