Other Parts Discussed in Thread: CDCLVC1310, AM6421

主题中讨论的其他器件:AM6421、

大家好、我们在其中一个基于 AM6421 处理器的设计中使用 CDCLVC1310 时钟缓冲器。 在参考 EVM 原理图“PROC101C (004)_SCH“时、我们在第 31 页上发现了一些与 CDCLVC1310 硬件电路相关的问题。 请参阅快照与 EVM 原理图以供参考:

1) 为什么我们在 XO 输出 (25MHz - U71) 上使用分压器 (R255 和 R245)?

2) 为什么我们对从 XO (25MHz - U71) 到时钟缓冲器 (CDCLVC1310RHBR - U70) 的路径使用过驱(交流耦合)模式?

据我所知、如果我们使用 CMOS 输出 XO (25MHz - U71)、最好使用旁路模式而不是过驱模式。 如果我在这里遗漏了一些东西、请纠正我。 此处是否有任何使用过驱(交流耦合)模式的具体理由?

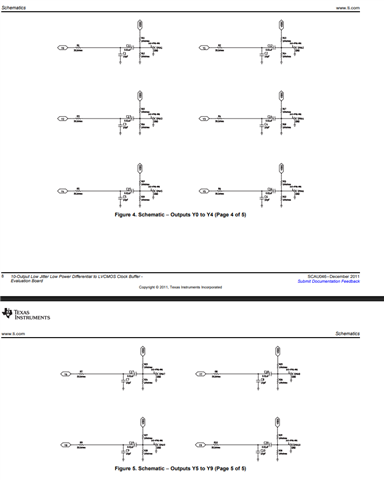

3) 在时钟缓冲器输出处、只有 Y5 至 Y9 的并行 RC 阻尼网络(C262 & R65 等)。 为什么 Y0 到 Y4 不相同?

此致、

Nikhil Jadhav