器件型号: LMK5C22212A

尊敬的团队:

我计划在电路板中使用 LMK5C22212ARGCT。

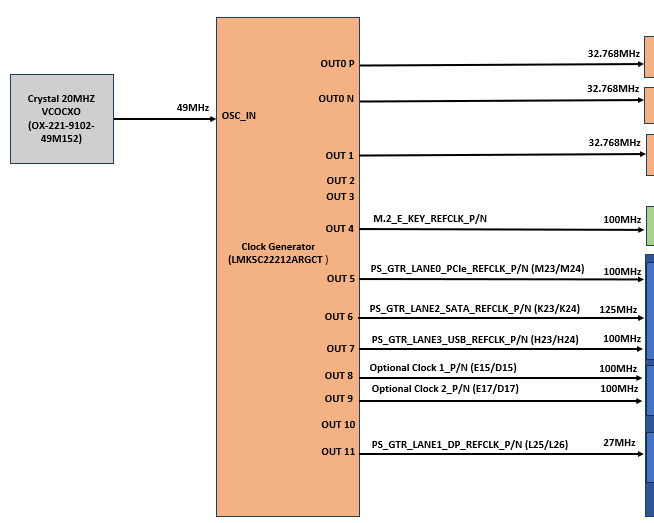

下面共享了电路板的时钟树。(请注意,仅检查输出时钟类型和频率,连接到 IC 的输出引脚可能不同,连接到原理图的输出引脚将是正确的引脚。)

我想要 7 个 LVDS 输出和 3 个 CMOS 输出。 抖动要求大于 100fs。

IC 输入仅通过 OXCO 晶振 (OX-221-9102-49M152 - 49MHz)。

还随附了时钟 IC 的原理图。

请查看并提供反馈、还请解决一些问题。

GPIO、SDA、SCLK 什么是 IO 电平?

对于 LVCMOS 1.8V 输出、是否存在任何硬件方面的更改、需要区分 2.5V 和 1.8V 输出

3.我的 OXCO 是 49MHz OX-221-9102-49M152,对我的设计来说是可以的。

我只对 IC 使用 OXCO 输入、IN0 和 IN1 可以保留为 NC?

仅提及 256MHz LVDS 输出在所有时钟输出上的电流时、电路的 3.3V 总功耗是多少(如数据表中所示)?

任何建议都是根据我的抖动要求连接我的输出。

此致、

Abhishek