主题中讨论的其他部件: CODELOADER

大家好,

请就以下与LMK0.3328万相关的问题向我提出建议。

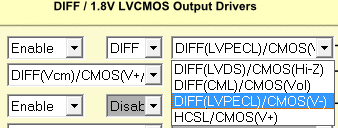

问题1. 当输出配置为时,CAN OUTN_P和OUTN_N输出相同的时钟极性

CMOS模式?

问题2. 当预期输出为1.8V CMPS时,VDDO_n是否可以使用3.3V电源进行操作

或限制为1.8V?

数据表描述如下。 这可能建议输出1.8V COMS时钟,

VDDO_x可以是1.8V,2.5V或3.3V。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

8.12 1.8 VDD_In / VDD_PLL1 / VDD_PLL2 / VDD_DIG = 3.3 V±5 % ,

VDDO_x = 1.8 V±5 % ,2.5 V±5 % ,3.3 V±5 % ,TA =-40°C至85°C,输出加载2 pF至GND

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

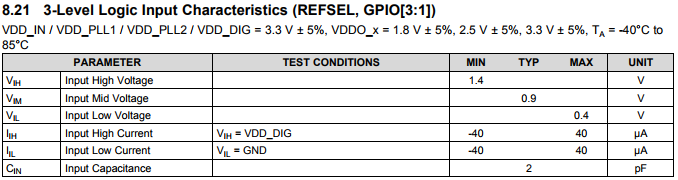

问题3. 您是否可以为我们提供尝试级输入引脚(如REFSEL,GPIO [3:1]引脚)的最小值和最大值。

数据表指定了VIM典型值。

但是,如果没有最小值和最大值,则无法设计应用程序板。

问题4: 该器件具有多个输出(OUT0_P/N至OUT7_P/N)和专用电源引脚VDDO_01/23/4/5/6/7。

如果未使用某些输出,则相应的电源针脚可以保持打开或必须保持打开

是否与供应有关?

问题5. 数据表指定了开机顺序。 VDD_In,VDD_DIG中是否有任何限制

VDD_PLL1,VDD_PLL2,VDDO_01/23/4/5/6/7?

只要它们在100毫秒内完成单声波,并且PD在100毫秒后完成,它们就能在零时间内正常运行

所有电源导轨?

Mita