大家好、

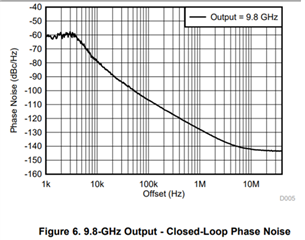

我的客户 正在尝试使用 LMX2592降低环路带宽。 数据表中的下图显示了~4kHz 闭环带宽:

此测试使用了哪些环路滤波器组件值?

客户正在尝试在环路滤波器中使用大电容器、并在小频率调整的情况下看到大环路增益变化。 PLLatimumSim 不显示他们正在测量的增益变化。 更高的环路带宽(~ 100kHz)不会显示此问题。

谢谢、

康妮

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Noel、您好!

客户 仍在解决他们看到的相位噪声问题。 他们需要帮助了解最后三个回读寄存器。 下面是 TICSPro 的屏幕截图。 我们如何解读 R68、69和70中的十六进制?

R68是 VCO SEL;R 69是 VCO CNTL、R70是 VCO DACISET。 我们看到 R68=0448、但对于8512.5GHz、R69=003C;对于7862.5GHz、R69=00AC。 对于8612.5、R70为0188;对于7862.5、R70为015F。

谢谢、

康妮

Noel、您好!

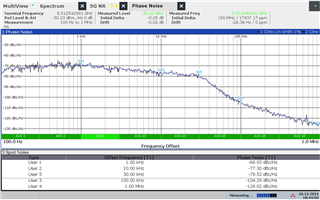

下图适用于客户 PCB 上的 LMX2592、并由其软件控制。 随附了电路板上器件的回读文件(请注意、显示的是 R69和 R70)。 这些寄存器设置与评估板的设置一致。 30kHz 偏移下的环路增益显示出接近10dB 的变化、而调谐频率变化仅为10%。 在评估板上使用相同的环路滤波器组件、它们不会看到这种巨大的增益变化。 是否有任何关于导致这种情况的建议?

低频、‘显示30kHz 时的相位噪声“峰值”:

下面显示了30kHz 偏移时的环路增益随调谐频率变化(黑色线迹为8512.5MHz、蓝色7962.5MHz):

编程看起来是正确的、但高频下衰减降低(更高的环路增益)会导致30kHz 偏移下的相位噪声更高。 请注意、在高频和低频之间、我们可以看到30kHz 偏移相位噪声在高端逐渐增加到10dB 唯一改变的是调整频率*。

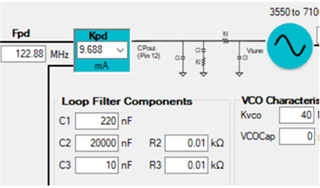

*最低频率确实会将相位检测器频率改变为所有其他频率的一半,以符合最小分频器设置。 环路滤波器:

当 PLL 被调谐至 PLL 以外的更高频率时、其系统中的任何内容都不会改变。 如有任何帮助解决此问题、我们将不胜感激。

e2e.ti.com/.../synth_5F00_regs_5F00_8512pt5MHz.txte2e.ti.com/.../synth_5F00_regs_5F00_7862pt5MHz.txt

尊敬的康妮:

FCAL_HPFD_ADJ 在8512.5MHz 设置下不正确、这可能会导致校准错误。

TICS Pro 和 PLL SIM 分别假设 VCO1和 VCO2为7862.5MHz 和8512.5MHz。 它们的 Kvco 相似、因此当 FPD 减半时、环路带宽应减半。 在 PLL SIM 中、7862.5Mhz 和8512.5MHz 时的环路带宽分别为8.04kHz 和13.63kHz。

然而、从寄存器回读中、在两个频率上选择了 VCO2 (来自校准)。

因此、7862.5MHz 时的环路带宽变为5.8kHz。 由于两个频率的相位裕度都大于75度、因此它们的相位噪声图实际上是相似的、因此我们无法从图中得出环路带宽差。

总之、尽管 FPD 和环路带宽不同、但这些频率下的相位噪声图应该相似。

关于"hump"、这可能是由于参考时钟。 在上述仿真中、未考虑参考时钟的相位噪声。 如果峰值是由参考时钟引起的、较小的环路带宽可以进一步减小峰值。

客户是否 在其电路板和 EVM 中使用了不同的参考时钟?