1.以前使用 CDCM6208是正常的。

SPI 总线配置如下:

REG[00] : 0x01b1;

REG[01] : 0x000c;

REG[02] : 0x0013;

REG[03] : 0x08f5;

REG[04] : 0x60CF;

REG[05] : 0x0023;

REG[06] : 0x0009;

REG[07] : 0x0023;

REG[08] : 0x0009;

REG[09] : 0x0003;

REG[10] : 0x0090;

REG[11] : 0x0000;

REG[12] : 0x0003;

REG[13] : 0x0090;

REG[14] : 0x0000;

REG[15] : 0x0003;

REG[16] : 0x0090;

REG[17] : 0x0000;

REG[18] : 0x0003;

REG[19] : 0x0090;

REG[20] : 0x0000;

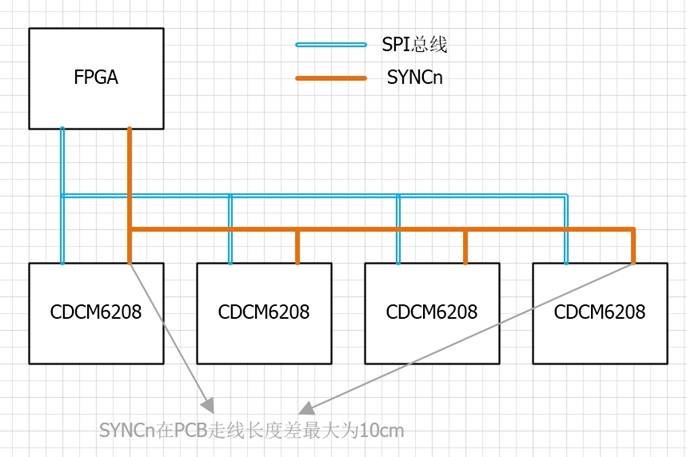

目前,不同部分之间的 SYNCn 信号由 FPGA 提供,该信号与 CDCM6208的每个部分链接在一起,而线长的差值约为10cm。 在 SPI 发送配置信息时、SYNCn 信号被下拉。 传输过程中的低电平;所有传输完成后、100ns 将生成上升沿。