您好

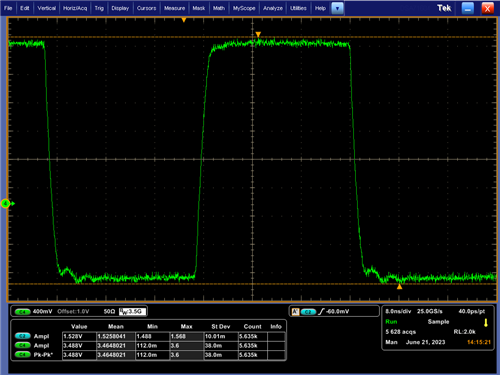

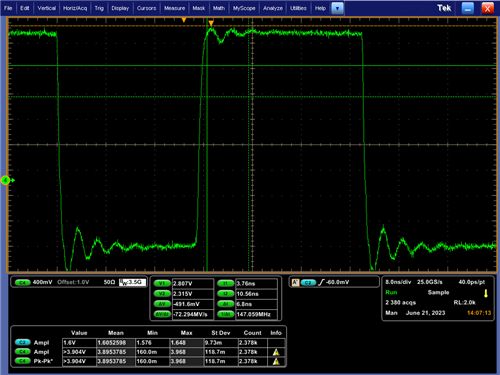

我们在 同一控制卡中使用两个 CDCV304时钟缓冲器、并且我们从这两个缓冲器输出获得不同的波形。

这2个缓冲器输出将连接到具有33欧姆终端的同一接收器。 对于1个缓冲器时钟输出、则没有振铃、而对于其他输出振铃、则存在。 并在下方附上了波形。

|

序号 |

网络名称 |

CLK 频率 |

驱动程序 |

接收器 |

串联 R |

从驱动器到 Rx 的 TL 长度 |

捕获的波形 |

|

1 |

CLK_10M_20M_1588_OCXO |

20米 |

CDCV1 |

Xilinx Kintex 7 FPGA |

33 Ω |

16.2英寸 |

|

|

2 |

CLK_125m_APLL_1588_FBCK |

125米 |

CDCV2 |

Xilinx Kintex 7 FPGA |

33 Ω |

3.8英寸 |

|

|

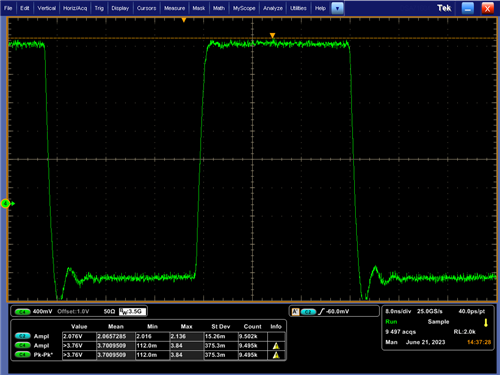

3 |

20MHz_PLL_OSC_CLK |

20米 |

CDCV1 |

RC 8A35036 SMU |

33 Ω |

9.6英寸 |

|

|

4 |

CLK_125m_PLL_1588_FBCK |

125米 |

CDCV2 |

RC 8A35036 SMU |

33 Ω |

4英寸 |

|

通过将端接电阻值更改为22欧姆、18欧姆、10欧姆、我们仍然会看到波形中因过冲和下冲而产生振铃。

我已经检查了 CDCV304 (CDCV1)的输入时钟、它没问题、并在这里附加了相同的时钟以供您参考。

数据表中提供的负载电路测试适用于70欧姆而非50欧姆的标准传输线路阻抗。

我们的 PCB 布线使用50欧姆阻抗进行布线。 您是否认为这可能导致了该问题?

请帮助我们了解振铃的原因。

谢谢

莫汉