您好!

我发现、当未上电的 LMK 输入在器件寿命周期的10小时内接收到信号时、性能不会下降。 虽然它也提到"短时间"、这是否意味着这些短时间总共达到10个小时? 如果是、这些短时间的最长持续时间是多少? 是否对 FIN0引脚进行了表征?

此致!

罗伯特·奥特加

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我发现、当未上电的 LMK 输入在器件寿命周期的10小时内接收到信号时、性能不会下降。 虽然它也提到"短时间"、这是否意味着这些短时间总共达到10个小时? 如果是、这些短时间的最长持续时间是多少? 是否对 FIN0引脚进行了表征?

此致!

罗伯特·奥特加

您好、Robert:

[报价 userid="567206" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345539/lmk04832-sp-performance-degradation-while-unpowered-for-fin0 ]虽然,它也提到"短时间",这是不是意味着这些短时间总共10个小时? 如果是,这些短时间的最长持续时间是多少?保证的最长持续时间为10小时以下、因此最长持续时间为10小时。 因此、每个周期不能超过10小时、不一定是累积的。

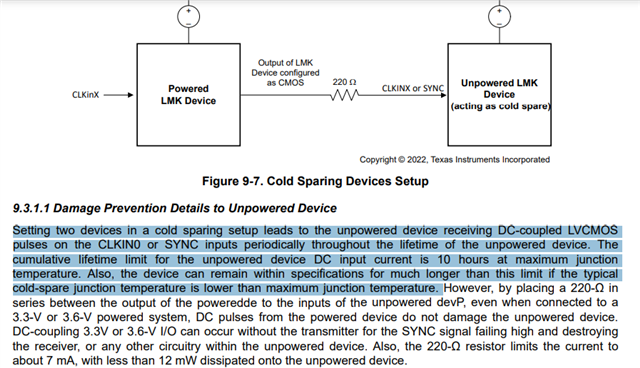

[quote userid="567206" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345539/lmk04832-sp-performance-degradation-while-unpowered-for-fin0是否为 FIN0引脚完成了特性描述?正确、但是对于所有 CLKinX 引脚、正如数据表9.3.1.1节中解释的那样。

此致!

安德烈亚

Robert、让我进入这里、因为我 认识到 https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1320249/lmk04832-sp-powered-off-max-input-voltage 中提出的一些问题。

首先,澄清:当我们说10小时的寿命,这是累积的。 达到该数值所执行的测试使用了在加速寿命温度下注入器件的恒定直流电流 、大约为7mA、并通过125°C 持续约1000小时(编辑:我的同事纠正了我、原来是125°C 持续1000小时、而不是125°C 持续100小时)、 因此、5mA 10hrs、125°C 的累积持续时间限制旨在提供 一个非常保守的限制、以考虑到我们测试的有限样本大小(考虑到成本、我们没有那么多航天级器件可供测试)。 如前面所述、在 较低的温度下、也可以标称延长持续时间、因为 当温度每升高~μ V 20°C 时、受影响金属层中可接受的电迁移限制会降低约一半。 该限制也适用于交流耦合输入、 但是、由于 未上电输入充当半桥整流器、具有高动态负载、包括 VDD 引脚上的所有元件(包括其他未上电的 LMK04832-SP 输入以及 LDO 或其他提供3.3V 电压轨的器件)、因此我们无法 为交流耦合情况提供强大的指导。 我们在数据表中插入此限值的主要原因是作为同步用例的直流耦合 SYNC/CLKin0、假设为非连续脉冲;因此、我不会假设直流耦合和交流耦合行为具有可比性。

第二、在回顾我的文章并查看原始 文档以了解我们如何得出数据表中的数据时、我实际上忘记了我们所关注的机制-它不是 ESD 布线、而是 通过输入缓冲器结构的基板电流路径。 ESD 元件的大小足以使这些元件无需太担心电迁移、 但其中一个 PMOS 输入缓冲器元件标称在 VDD 处具有基板偏置、因此如果器件未通电、则会存在从 PMOS 的漏极到浮动基板节点的路径。 这并没有改变我的结论、我只是想澄清正确的受影响要素。

回答您的问题: 我们没有 直接测试 Fin0的累积寿命应力。 我之前给了您一个关于这一点的答案、但我可能不清楚、因此让我澄清一下原因:

如果 Fin0输入结构中的金属路径的大小与 Fin1/CLKin1或 CLKin0不同、 并且输入电压足够高、导致 进入 Fin0的输入电流(mA 范围)具有潜在破坏性、那么上述推理可能是无效的; 或者、 如果温度足够高、以至于二极管的正向电压显著降低(没有模型的话、这一点很难预测、但它远高于建议的125°C 限值)。 因此、我可以自信地告诉您、在本例中、10小时寿命限制不是适用的问题、 由于您之前的 E2E 帖子中所述的 Fin0输入幅度不足以在任何类型的输入结构中获得可能会产生电流基板路径的 mA 标度电流、无论最终是什么结构、都是如此。

在未供电的 Fin0中传输±300mV 以上的值时、 我不知道 Fin0是否会受到电迁移问题的影响-我的担忧会与输入振幅成指数级增长(以及随后流入基板路径的电流)、也许会随着温度而增加(无论值如何)。

很抱歉,如果这些答案有些不满意的话。 LMK04832-SP 在设计周期中没有考虑冷备用或未上电的输入使用情况、因此我们最终发现在这样一个事实之后、 但是、除了非常保守的限制和一些与 绝对最大额定值一致的模糊限制外、限制其他任何内容变得很复杂。 未来的设计肯定会 将冷备用或失效防护输入设计考虑在内。