您好、TI 专家。

我的客户正在使用 LMK04806向其他 DAC 和 FPGA 输出多种类型的时钟。 输入时钟为100MHz。

客户发现存在如下所示的1.2G 相位噪声、可以通过更换新的 LMK04806来解决该问题。 客户怀疑 IC 本身有问题。

您能帮助检查原理图和布局吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 专家。

我的客户正在使用 LMK04806向其他 DAC 和 FPGA 输出多种类型的时钟。 输入时钟为100MHz。

客户发现存在如下所示的1.2G 相位噪声、可以通过更换新的 LMK04806来解决该问题。 客户怀疑 IC 本身有问题。

您能帮助检查原理图和布局吗?

您好、William、

下面是我的客户提供的 LMK04806配置文档。 他们可以在自己的电路板中实现时钟锁定、而不能在 TI EVM 中锁定时钟。

e2e.ti.com/.../LMK04806-config-which-can-not-be-locked-in-TI-EVM.tcs

Gary、

通过对 EVM 进行测试、我能够找到导致 PLL 无法锁定的原因。

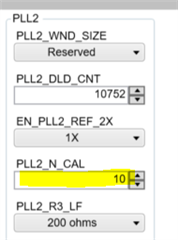

我注意到 PLL2_N_CAL 设置为12、此时它应与您在 PLL2 GUI 页面中设置为10的 PLL_N 匹配。

当只将 PLL2_N_CAL 写入12时、锁定没有 丢失。 但是、当写入 PLL2_N_CAL 至12然后重写所有其他寄存器时、会失去锁定、因为 VCO 被触发进行重校准并且 PLL2_N_CAL 和 PLL2_N 的 值与它们应该的值不同。

如果您需要更多帮助、请告诉我。

此致、

将会