Other Parts Discussed in Thread: LMX2572, LMX2572LP, LMX2572LPEVM, LMX2581

主题中讨论的其他器件:、 LMX2581、LMX2572

有关 PLLatinum Sim 的更新。

我使用 LMX2572LP 运行仿真。

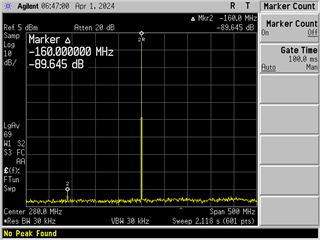

我运行了 PLL 仿真并保存了结果(图1)。

然后我加载结果并再次输入280MHz、环路带宽和相位裕度值会发生变化(图2)。

哪个结果是正确的?

我从网站下载了 PLLatinum Sim (图3)、但情况保持不变。

我想知道正确的结果、因为我将在不久的将来开始 PCB 设计。

此致、

横内明彦

图1

图2

图3