主题中讨论的其他器件:LMX2594、

工具与软件:

您好!

我们无法 在数据表中提供有关 LMX2582的 VCO 内核范围的任何信息、LMX2594数据表中提供了该表、您能提供吗? 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Zhang:

不错的地方 这是我们应该在下一次 DS 修订时包含的内容。

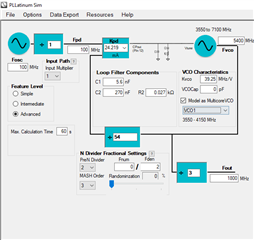

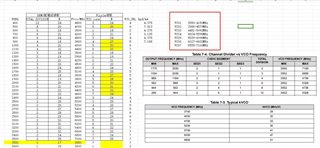

有关 LMX2582器件配置文件、请参阅 PLLatinumSim 中的以下内容:

VCO1:3550MHz、-4150MHz

VCO2: 3986MHz -4579MHz

VCO3:4481MHz、-5092MHz

VCO4:4924MHz、-5596MHz

VCO5:5535MHz、-6096MHz

VCO6:6027MHz、-6632MHz

VCO7:6555MHz、-7100MHz

此致、

Vicente

您好、Vicente、

LMX2582有一些问题:

1.我们根据数据表使用 LMX2582、并记录 N 和 FVCO、但数据表和 PLLATINUMSIM 之间有一些不同、我们不知道哪一个是正确的?

2.请告知 LMX2582的空腹锁定时间? 我们在 PLLATINUMSIM 中读到它大于10us;

3. 在配置 LMX2582的初始化时、我按照规格表中的说明配置快速锁定功能、但无法锁定。 您能帮我找出问题所在吗?

尊敬的 Zhang:

您的 PLLatinumSim 结果和 TICSpro 结果之间的差异是 VCO 频率的差异造成的

我插入了这些值、以下两种组合都可能导致500MHz 输出:

这两种配置都是有效的配置 、但 如果您希望优化相位噪声性能、请始终使用能够产生尽可能低的 N 分频器值的配置。

通常、我们始终希望通过具有最大 FPD 频率来使用最低 N 分频器-为此、请使用倍频器将 FPD 频率从100MHz 增加到200MHz。

请参阅以下主题、了解如何缩短 LMX2582的锁定时间:

https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/680377/lmx2582-decrease-lock-time-possible-negative-effects

此致、

Vicente

此致、

Vicente

尊敬的 Zhang:

我怀疑频率实际上可能不稳定。

您是否有能够测量频率与时间的设备?

请参阅 Noel 的最后一个答复、以便更好地了解我所说的内容。

https://e2e.ti.com/support/clock-timing-group/clock-timing-internal/f/clock-timing---internal-forum/1384021/lmx2572lpevm-lock-time/5320658#5320658

如果我们查看宽带的频率、一个器件可能会出现"锁定"状态、而实际上输出频率仍然稳定(模拟稳定时间)。

我们只能使用窄带直接确定器件何时处于锁定检测变为高电平的阈值范围内。

这可以解释为什么 LD 需要更长的时间才能变为高电平。

此致、

Vicente