请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX1214 工具与软件:

您好!

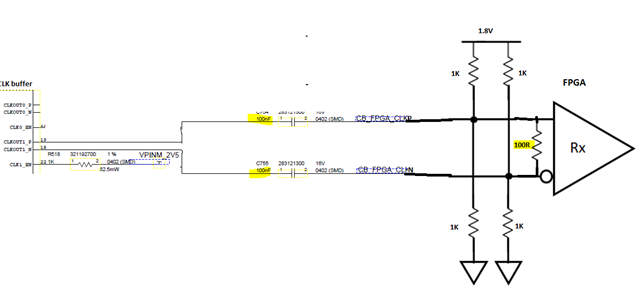

时钟缓冲器的输入频率为1800MHz、我们计划将 CLKOUT 引脚连接到 FPGA、并将其设置为 225MHz 的输出频率。

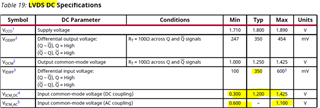

CLKOUT 引脚似乎与 CML 标准相似。 FPGA 可以支持 LVDS、如下所示:

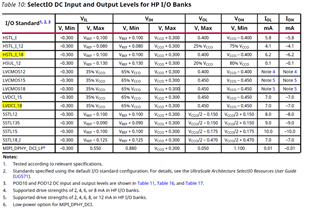

它还支持下面重点介绍的差分标准。

那么、您能否分享在 FPGA 输入端使用哪种标准来满足 CLKOUT 的输出标准?

另外、请建议这两个接口标准之间需要使用哪种类型的终端?

谢谢