主题中讨论的其他器件: LMK05318B

工具与软件:

您好、BU、

我收到了客户的2个问题。

1、在 OUT0-7上出现从上电到输出信号的启动时间

2、从 PRIREF 信号输入到锁定的锁定时间以及输出信号的显示方式

尤其是、客户想知道 PRIREF 的1PPS 条件。

您是否有任何数据可以回答这些问题?

此致、

Yuki

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、BU、

我收到了客户的2个问题。

1、在 OUT0-7上出现从上电到输出信号的启动时间

2、从 PRIREF 信号输入到锁定的锁定时间以及输出信号的显示方式

尤其是、客户想知道 PRIREF 的1PPS 条件。

您是否有任何数据可以回答这些问题?

此致、

Yuki

尊敬的 Yuki:

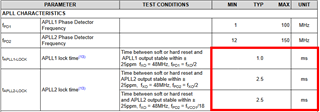

请参阅数据表中的 APLL 锁定时间。 这是启动和稳定输出时钟之间的时间。

输出到锁相到1PPS 信号所需的时间可能是几分钟。 在1PPS 锁定之前、输出与 XO 输入相位对齐。 1PPS 锁定开始后、输出将在相位上从 XO 输入相位稳定切换到1PPS 输入相位。 在转换(保持至1PPS 锁定)期间、输出不会受到干扰、也不会发生相位中断。 这称为"无中断切换"。

此致、

Jennifer

尊敬的 Yuki:

有快速锁定。 但是、这取决于输入和输出之间"锁相"的定义。 是否需要多长时间才能在输入和输出之间获得接近0ppm 的相位误差? 或者、输出开始跟随输入需要多长时间?

DPLL 频率在几秒钟内将输出锁定到1PPS 输入。 锁频时、输出与输入的频率精度相同。

在相位方面、我们通常将锁相定义为输出相位在输入相位之后开始的点。 DPLL LOPL (相锁丢失)状态信号提供了进一步的定义。 DPLL_LOPL = 0表示 DPLL 已锁相 根据定义的锁相和解锁阈值寄存器设置 DPLL_LOPL=1表示 DPLL 的相位解锁超出阈值。

总之、如果客户将相锁定义为1PPS 输入和输出之间的0ppm 误差、则需要几分钟时间、因为所需的 TDC 速率为1Hz、DPLL LBW 为0.01Hz、这会降低相位校正的速率。

如果客户将相锁定义为输出开始跟踪1PPS 输入时、则会在不到一分钟的时间内开始。

此致、

Jennifer

尊敬的 Yuki:

LMK05318B 具有用于 DPLL 的数控振荡器(DCO)功能。 DCO 使用户能够通过精细(40位)递增或递减对 DPLL 分子进行外部频率和相位调整(它们手动进行)。 例如、客户可以在 LMK 输出需要10ppb 的偏移量时使用 DCO。 在本示例中、基准输入和 LMK 输出之间的频率/相位差变为10ppb。

如果进行 DPLL DCO 调整、则输出的相位和频率都会受到影响。 这两者无法分离。

如果使用 DPLL DCO、则锁相时间不受影响、因为必须先锁定 DPLL 才能使 DPLL DCO 工作。 DPLL 锁定后应用到 DPLL 的偏移(进而影响 APLL 和输出)。

此致、

Jennifer