Other Parts Discussed in Thread: ADS5409

工具与软件:

嗨、团队:

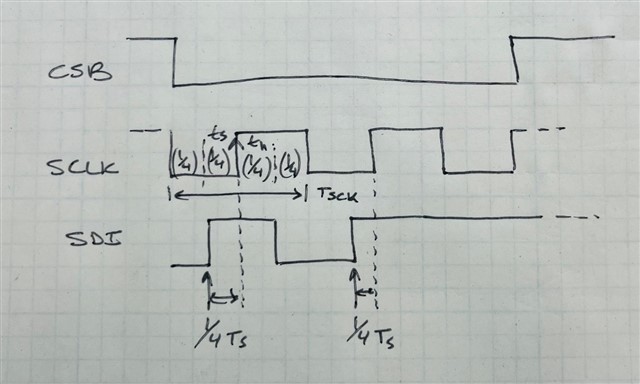

我们的项目使用与 ADS5409芯片连接的 Xilinx Artix 7 FPGA。 在这里、FPGA 充当 SPI 主器件、ADC 芯片充当从器件。 我们需要使用以下限制来限制 SPI 接口

SET_INPUT_DELAY -clock clk_sck -max [expr $TCO_max +$tdata_trace_delay_max +$tclk_trace_delay_max][GET_PORTS IO*_IO]-clock_fall;

SET_INPUT_DELAY -clock clk_sck -min [expr $TCO_min +$tdata_trace_delay_min +$tclk_trace_delay_min][GET_PORTS io*_io]-clock_fall;

ADC 数据表中未提供 SPI 接口输出时钟的最小值和最大值(TCO_min 和 TCO_max)值。 您能否告诉我们必须为 TCO_max 和 TCO_min 分配哪些值?

提前感谢。