工具/软件:

我们观察到 100–200LSB 范围内的计数变化、即使在输入通道短路的情况下也是如此。 这表明测量系统中存在潜在的噪声、偏移或稳定性问题。 请建议各种方法来尽量减少这种变化并提高测量精度。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好 Shushant、

欢迎来到 TI 的 E2E 论坛! 感谢您发送编修。

我有一些跟进问题:

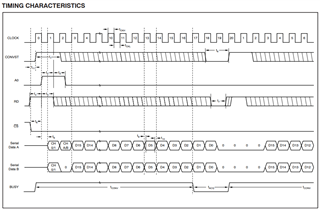

根据我在代码中看到的结果、数据似乎应该被正确解码回、但我想确认 SPI 协议配置

[引述 userid=“657744" url="“ url="~“~/support/data-converters-group/data-converters/f/data-converters-forum/1524408/ads8361-we-found-count-variation-in-reading/5860617 #5860617“] SPI1CONbits.CKE = 1; //CLK 边沿(从有效时钟状态转换到空闲时钟状态时输出数据发生变化)SDO 上的数据在 上升沿转换、在 下降 沿有效。 设置 SPI1CONbits.CKE =1 是否配置为在下降沿读取数据(从工作到空闲时钟阶段)、或者这是否使其读回相反的转换?

此致、

Yolanda

e2e.ti.com/.../R_5F00_DATA_5F00_2_5F00_120000.xlsx

我们获取的数据计数与变体和图形相同。

感谢您发送编修。

我认为代码看起来不错、与 RD 引脚同步应该可以正常工作。

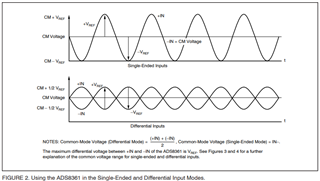

查看您的原理图、您能否确认差分放大器的输出信号是什么样子? ADS8361 似乎当前配置为伪差分模式。 按此方式使用应该没问题、但确实要求 AIN+上的信号仍然保持 VREF 的共模。 由于差分放大器的电源为+/–5V、并且这些差分放大器的 REF 引脚连接到 GND、 我想确保它们仍然存在偏移、以便保持在共模范围内?

在使用内部基准时、只要 LK1 和 LK18 短接、它也应该很好。

此致、

Yolanda

我们使用单端模式(仅具有 AOUT 的 A0 和 B0)。 连接到基准引脚和基准链路的 AIN-端接也会缩短、因此我们获得 2.5V 基准电压。 这就是我们的计数超过 32767 的原因。

我们在 10KHz 下采集了 60000 个样本、SPI 速度为 2MHz。

您对计数变异有何体验?? 数据转换的容差范围是多少?

如果您有任何 PCB 板布线示例、我们将在这些示例中统计而不会有差异、请分享这些示例?? 或者您观察到相同类型的变化??

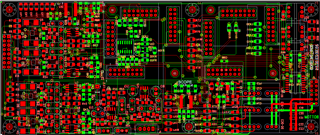

我分享了 PCB 布线图像如果您有任何建议、请提供您的意见。

您好 Shshan、

我们以 10KHz 采集了 60000 个样本、SPI Speed 为 2MHz。

此信号的振幅是多少? 它是否也有 2.5V 的共模? 您能在示波器上分享一下这个情况吗

您对计数变化有何体验? 数据转换的容差范围是多少?

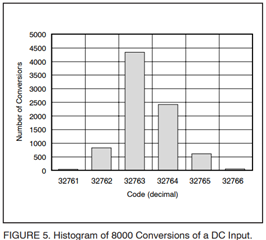

使用直流输入时、代码扩展约为 ±2.5 个代码/lsbs。

。

请说明一下 ADC 以及 ADC 周围的任何元件位于何处? 如果有可用的原理图、也会有所帮助。

输入是否有 RC 滤波器? ADC 输入的驱动电路是什么?

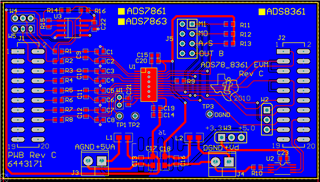

布局可以很简单、此器件不存在高速问题。 ADS8361EVM 的布局 (U1 是 ADS8361)

此致、

Yolanda