工具/软件:

我正在恢复一个旧的帖子,我在几个月前,我失去了轨道.

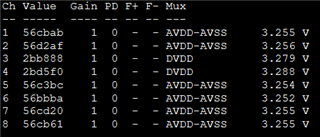

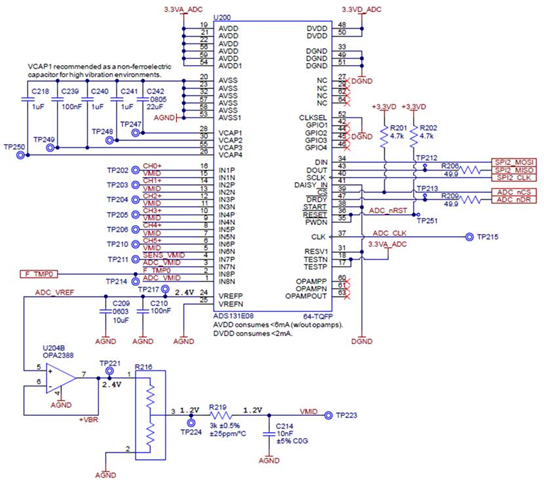

我们的设计实现了 ADS131E08 ADC 的完整 24 位范围。 我们预计完整范围为+/- 2^23 位=+/–8,388,608。

我们使用的正输入电压范围为 0 ~ 2.4V、每个通道都有 1.2V 的固定负电压。 这样、差分输入电压范围为+/–1.2V、通过使用内部 ADC 增益= 2、我们可实现约+/–2.4V 的差分输入电压范围。

简而言之、我们的问题是、我们可以看到 ADC 值在达到差分输入范围之前卡住。 当我们通过在正输入通道上施加 2.4V 或 0V 来强制输入达到饱和时、ADC 输出不会达到+/–8M。

我们在两个设计上都看到了这种行为。 在第一个中、我们为 ADC 提供 3.3AVDD、将 AVSS 连接到 0V GND。 在上、第二个 AVDD 连接到 3.0V 而不是 3.3V。 在第一种情况下、我们确实看到+8388607 位于正极末端、但我们在负极末端永远不会达到–8388608 在第二种情况下、我们不会在负端或正端达到 8M。

我能理解为什么会发生这种情况、以及我们可以采取什么措施在我们的用例中利用完整的 24 位范围吗?

要回答 Dale Li 在原始帖子中提出的问题...

1.我不确定校准 或偏移误差指的是什么。 在第 1 种情况中、多个电路板/芯片的饱和值相当一致。 在 PGA = 1 时、我们仅在正输入端施加 0V 时达到约–4M 计数。

| 情形 1 | |||||

| 增益 | 1. | 2. | 4. | 8. | 12 |

| 负代码 | –4182489 | 5576058 | –6685939 | –7445348 | –7717432 |

| 正代码 | 8388607. | 8388607. | 8388607. | 8388607. | 8388607. |

2.对于案例 2 --是的、3.0V 电源是设计这一部分的唯一显著差异。

| 情形 2 | |||||

| 增益 | 1. | 2. | 4. | 8. | 12 |

| 负代码 | –4182489 | 5576058 | –6685939 | –7445348 | –7717432 |

| 正代码 | 6272517 | 8373916 | 8388607. | 8388607. | 8388607. |