Other Parts Discussed in Thread: DAC5662, DAC5672A, DAC5652, DAC5672

主题中讨论的其他器件: DAC5652、 DAC5672、DAC5662

工具/软件:

您好、

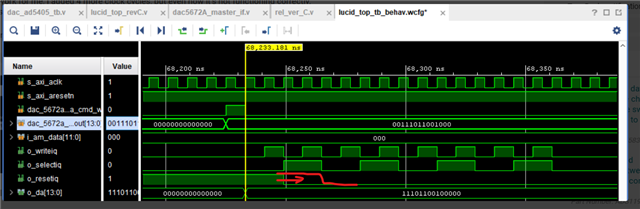

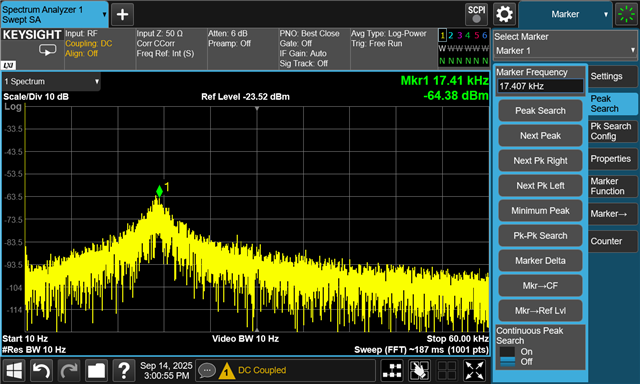

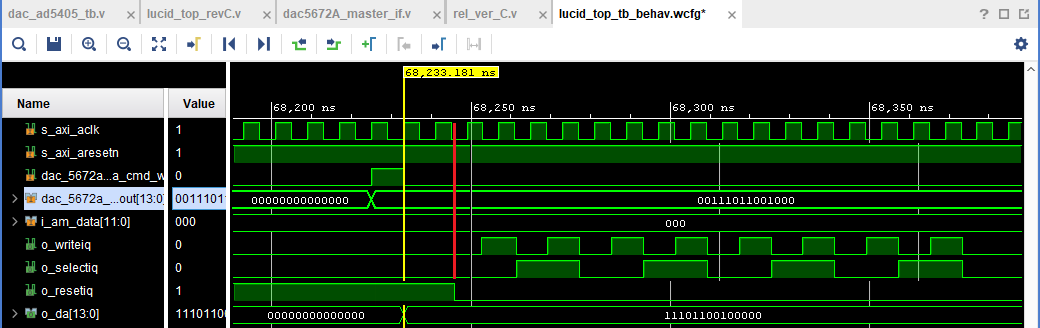

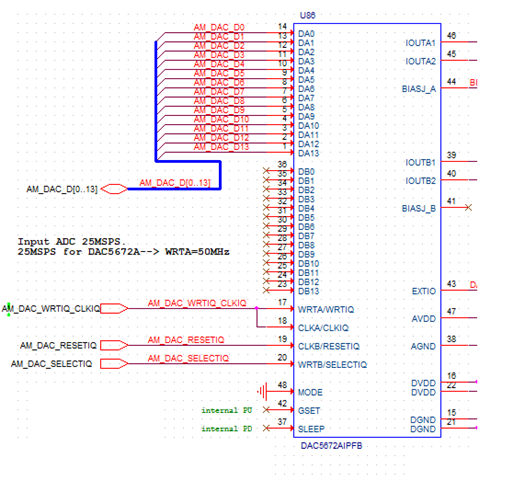

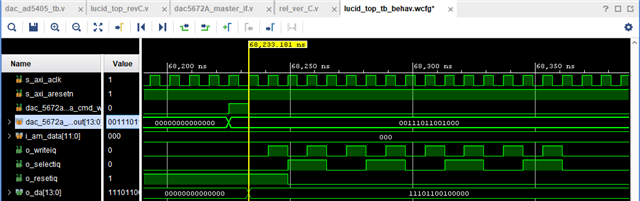

我尝试在交错模式下使用 DAC5672A。

我正在将相同的数据写入两个通道。

WRTIQ 和 CLKIQ 连接到同一条线路。

据我所知、在 WRTIQ 和 CLKIQ 的第四个上升沿、应输入数据。

当它对我来说不起作用后、我增加了 4 个时钟周期、但现在仍然无法正常工作。

问题是什么?

我明白了吗?

我还使用了以下文档(DAC5652、DAC5662 和 DAC5672 交错数据模式)。

e2e.ti.com/.../dac5672a_5F00_X2_5F00_Interleaved_5F00_Mode-.pdf

谢谢你

Gil