“线程”中讨论的其它部件:DAC38J84, LMK04828

你(们)好

我正在使用 DAC38J84 EVM。

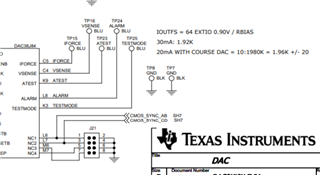

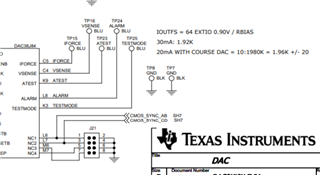

数据表中提到时钟和 Sysref 标准是 LVPECL (交流耦合)。

但在 EVM 架构中,Sysref 是 DC 耦合。 因此,推荐 的标准是 LCPECL 。

现在,我错误地将 LVPECL16从 LMK04828连接到 DAC。 这是否会损坏 sysref 路径?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

我正在使用 DAC38J84 EVM。

数据表中提到时钟和 Sysref 标准是 LVPECL (交流耦合)。

但在 EVM 架构中,Sysref 是 DC 耦合。 因此,推荐 的标准是 LCPECL 。

现在,我错误地将 LVPECL16从 LMK04828连接到 DAC。 这是否会损坏 sysref 路径?

大家好,Pavan,

这可能会影响 DAC 的长期使用寿命可靠性,并影响 DAC 注册 SYSREF 脉冲的能力,这是因为在共模模式下发生了大变化。 请参阅下面的申请说明了解详细信息:

帕万

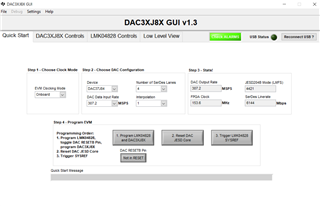

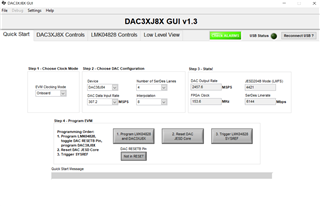

请确保您正在执行随附文档中的步骤。

此致,

吉姆

你好,Jim

我将 DAC38J84与定制 FPGA 板(包含一些第三方 FPGA)一起使用。

我已附加了 DAC 配置。 JESD LinkUp 正在使用这些配置

e2e.ti.com/.../4863.DAC_5F00_config.cfg

我发现我的 DAC 只能在 K =32和 RBD >20下工作。

它不能与 K=16和任何 RBD 配合使用?

这意味着什么?

这是否 意味着 FPGA 到 DAC 芯片路径存在大量偏差?

我的理解是否正确?

你好,Jim

我认为我共享了错误的配置文件。 很抱歉

L = 4

K = 32

F = 2

因此,在我的理想状态下,K*F >17=> K 可以高于10。 因此 ,如果使用 K =10,我的配置也必须工作?

嗨,Jim,

问题不在于 K 的值

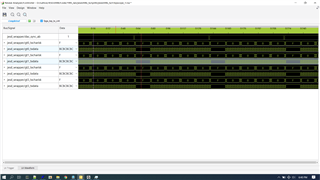

即使在 K =32时,我的同步也在切换

但同步信号在1个时钟周期中较低,并且再次较高

DAC 中没有错误

假设同步是 low....it,我们必须等待发送 BC 字符,但在这里,同步字符再次变低时,它就会变高。

因此,我的 IP 正在不断发送 CGS 和 ILA 数据

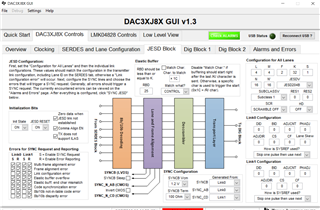

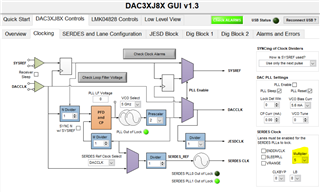

我正在使用 CMOS_SYNC_AB。

J21芯片是否会造成问题?

嗨,Jim,

问题不在于 K 的值

即使在 K =32时,我的同步也在切换

但同步信号在1个时钟周期中较低,并且再次较高

DAC 中没有错误

假设同步是 low....it,我们必须等待发送 BC 字符,但在这里,同步字符再次变低时,它就会变高。

因此,我的 IP 正在不断发送 CGS 和 ILA 数据

我正在使用 CMOS_SYNC_AB。

J21芯片是否会造成问题?

我认为问题在于 FPGA 和 DAC 之间的同步路径。

你好,Jim

1. K =32

2. F =2

3. Sysref 频率= 9.6 MHz

e2e.ti.com/.../dac_5F00_x8-_2D00_-config.cfg

完成所有这些配置后,我将重置 DAC JESD 核心

问题:

我正在使用 Sync_AB。

SYNC_AB 在一个时钟周期内会变得很低,并立即变得很高

FPGA 时钟= 153.6 MHz,K = 32,F = 2

请检查我的配置

帕万

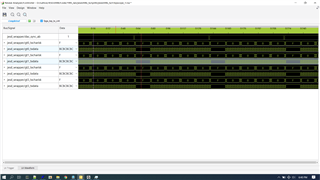

我在上面的屏幕截图中看不到0xBCBC 字符。 我使用我们的模式生成器板运行您的设置时没有任何问题。 配置文件已附加。 当您单击清除和读取警报时,警报选项卡会显示什么? 您是否有任何使用 LVDS 同步的方法?

此致,

吉姆

你好,Jim

同步切换问题已解决。 FPGA 固件存在问题。

同步为“高”后,我们无法发送正确的 ILA 数据。

感谢您的支持。

现在在 x8插值时,我的 JESD 链路工作正常,但在 x1插值时它不工作。

x1和 x8的 FPGA 代码是否相同 ?

FPGA 时钟= 153.6 MHz

FPGA Sysref = 9.6 MHz

DAC 克隆=307.2 MHz

DAC Sysref = 9.6 MHz

已 附加 x1的配置。

请核实这些情况。

e2e.ti.com/.../4421_5F00_K_5F00_32_5F00_Fs_5F00_312p5.cfg

您还可以解释乘法器和 VRange 的操作

线路速率= SERDES CLK *乘法器* 2?

(2是半价的蜂甲用途)?

帕万

在将 RBD 更改为30之前,我遇到了相同的问题。 请参阅随附的文件。

此致,

吉姆

帕万

您应该能够使用 GUI 来确定此值。 随函附上一份我认为也会有帮助的文件。

此致,

吉姆

e2e.ti.com/.../2084.DAC38J84-Clock_2C00_-PLL-and-SERDES-Configuration.docx