Other Parts Discussed in Thread: ADS1602

大家好,团队

我的客户有一些问题需要询问,请参阅下面的问题。

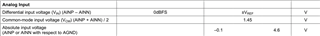

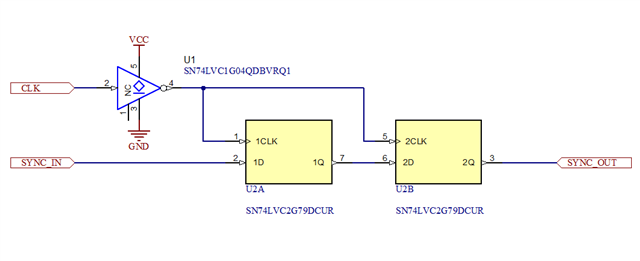

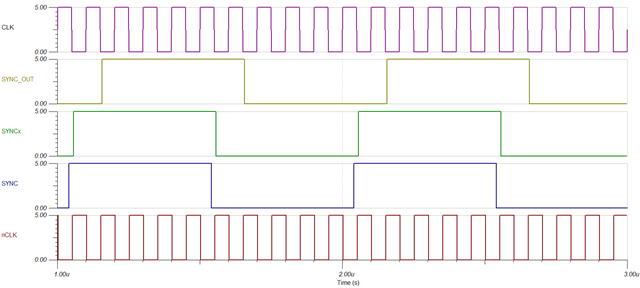

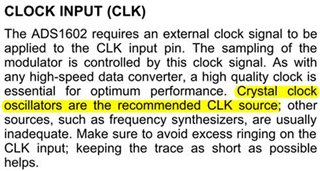

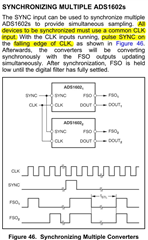

) 建议使用 OSC 进行 CLK 输入,如果有多个 ADS1602,则 CLK 应并行连接到每个 IC。 此 CLK 是否需要在 ADC 之后连接到控制 IC? (例如 MCU,FPGA,CPU...等)

2) 基于上述问题,如果在 ADC 之后 CLK 未连接到控制 IC,控制 IC 如何在 CLK 下降边缘发送同步信号?

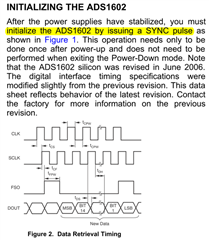

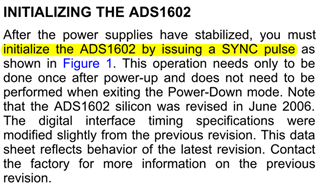

(第3条) 当系统通电时,控制 IC 只需要发送同步,然后 ADS1602将单独发送 FSS/SCLK/DOUT? CLK,SCLK 和 SYNC 之间的顺序是什么?

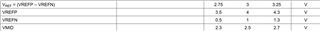

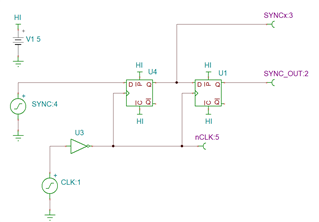

4) ~规格,AINP&AINN 的输入电压是否只能为+2.95 µ A-0.05V?