线程中讨论的其他部件:ADC12J4000, TRF3765, LMK0.4828万, TSW14J56EVM, ADS5562, ADS5562EVM

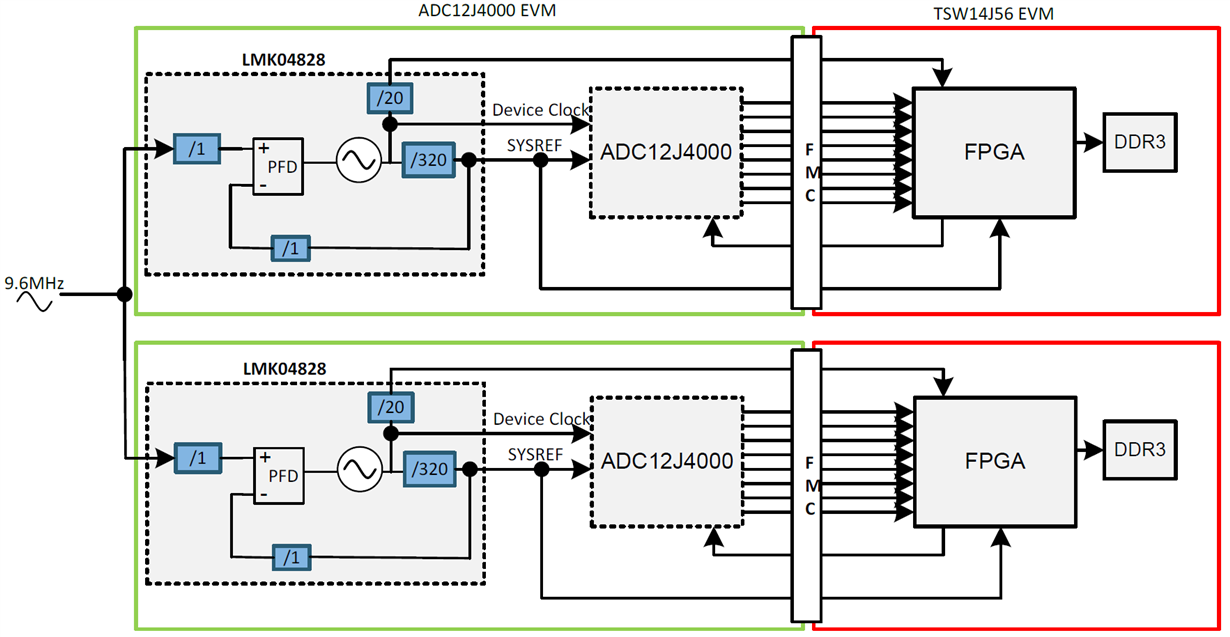

我正在开始使用2个具有外部时钟的ADC12J4000EVM的过程。 最终我想升级到4Ghz,但首先我会对1GHz感到满意。 我有一个EVM板,其帽已按照“ADC12J4000 ADC 12位4 GSPS用户指南”中的规定移动,另一个未修改。 未经修改的主板可与内部时钟和GUI上可用的任何预定义频率配合使用。

只需一个电路板和外部时钟即可完成初始测试:

使用外部时钟时,我根本没有读数,而 是得到一 个“超时错误”窗口,其中有3个可能的原因。 1) ADC正在重置,2) ADC EVM时钟未接收(但D2和D4正在闪烁)或3)未建立同步-这似乎最有可能是因为D2和D4闪烁但不同时且D1和D3打开

我的理解是,如果低于3.1GHz,则外部时钟需要相同的频率,因此我要在EVM板上拆分单个射频信号时钟,并从相同的射频源(两个输出都验证为2.2Vpp)输入DEVCLK和LMKCLK。 这不正确吗? 我是否必须使用同时同步的4Ghz和2GHz RF时钟来实现外部时钟工作?

谢谢

BART