您好,

我正在将ads1118与Arty A7-100T (FPGA)板连接。我已完成以下配置:-

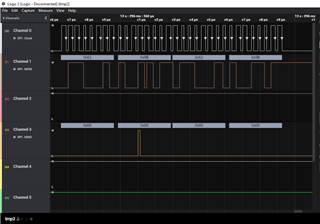

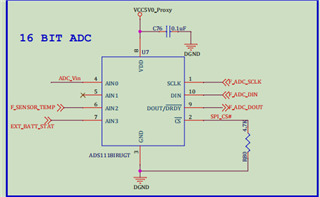

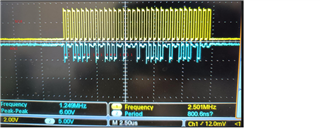

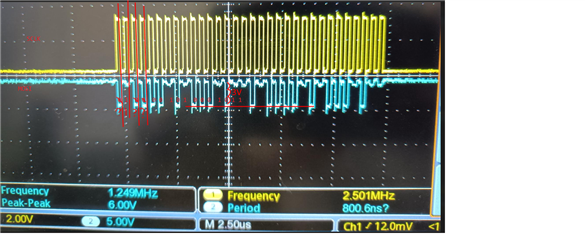

1.ADS1118以2.5MHz的clk速度运行,VDD为5V。

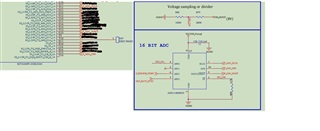

2.i在 温度模式 和连续模式下配置设备,配置寄存器=x629B。

3.FSR=+- 4.096 ,数据速率=128SPS,启用上拉模式,AINP为AIN2,AINN为。

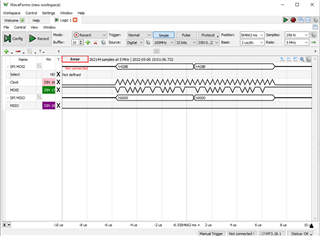

我正在使用32位SPI通信并将配置寄存器写入x629B 629B读回0

我有几个问题

1.在连续模式下检索数据是否需要一些延迟?

2.ca我希望从最初 的32位时钟链得到转换结果 ?

3.我的配置是否错误

谨致问候

Ajay