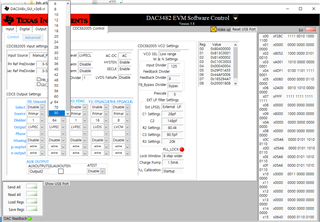

Other Parts Discussed in Thread: CDCE62005, DAC3482, DAC3484

主题中讨论的其他器件: DAC3482EVM、 CDCE62005、 DAC3482、 DAC3484、 DAC3484EVM

您好!

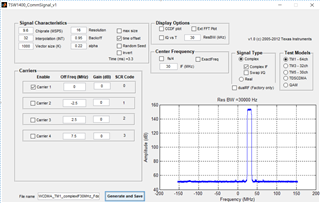

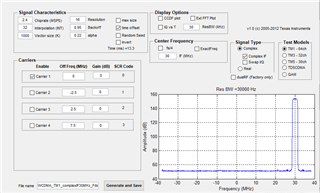

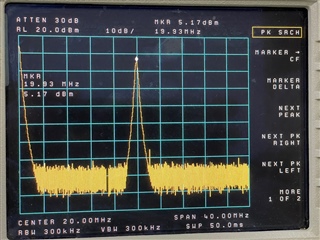

我需要 在 TSW1400EVM 中使用图形文件。

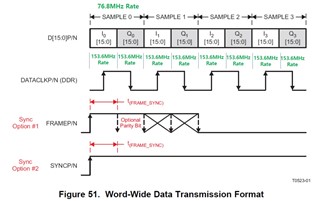

提供的模式文件为 WCDMA_TM1_badiIF30MHz_Fdata307.2MHz_1000.TSW、但需要将 Fdata 更改为76.8MHz 的 WCDMA_TM1_badiIF30MHz_Fdata76.8MHz_1000.TSW。

谢谢你。