主题中讨论的其他器件: DAC3482EVM、 CDCE62005、 DAC3482、 DAC3484、 DAC3484EVM

您好!

我需要 在 TSW1400EVM 中使用图形文件。

提供的模式文件为 WCDMA_TM1_badiIF30MHz_Fdata307.2MHz_1000.TSW、但需要将 Fdata 更改为76.8MHz 的 WCDMA_TM1_badiIF30MHz_Fdata76.8MHz_1000.TSW。

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我需要 在 TSW1400EVM 中使用图形文件。

提供的模式文件为 WCDMA_TM1_badiIF30MHz_Fdata307.2MHz_1000.TSW、但需要将 Fdata 更改为76.8MHz 的 WCDMA_TM1_badiIF30MHz_Fdata76.8MHz_1000.TSW。

谢谢你。

Jong-min、

转至 TI 网站上的 TSW1400EVM 产品文件夹并下载以下软件:

有关如何使用这些工具创建您请求的测试模式的说明、请参阅随附的文档。

此致、

Jim

不确定。 试试吧。 如果遇到问题、我可以为您创建此文件。 请告诉我应该在随附的幻灯片上使用哪些设置。

如果没有 Matlab 许可问题、我认为我可以在图形发生器中生成信号。

在下面的模式中创建了 CDMA_EVDO/CommSignal/LTE/MCGSM/MultiTonePattern 的哪个项目?

C:\Program Files (x86)\Texas Instruments\High Speed Data Converter Pro\Test Files\WCDMA_TM1_SPICIIF30MHz_Fdata307.2MHz_1000.TSW

谢谢你。

感谢您的回复、很抱歉您的回复很晚。

我想依次验证《TSW1400EVM 和 DAC3482EVM 用户指南》中确认的内容、然后使用我想要的选项检查结果。

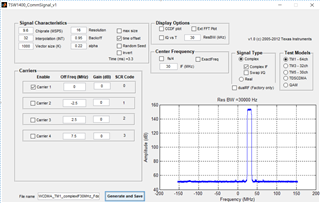

如图1所示、如果您创建图形(307.2MHz Fdata)并设置寄存器、则中心频率90MHz 信号将从 EVM 板输出中输出。

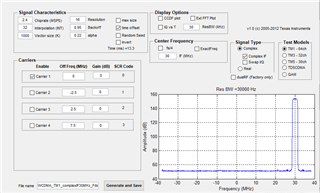

但是、如果您如图2所示创建图形(76.8MHz Fdata)并将寄存器0值从0xF28C (插值 x4)更改为0xF88C (插值 x16)、则不会输出。

当 Fdata 速率从307.2MHz 降低到76.8MHz 时、是否有任何需要额外修改的寄存器?

e2e.ti.com/.../DAC3482_5F00_FDAC_5F00_1228p8MHz_5F00_4xint_5F00_NCO_5F00_60MHz_5F00_QMCon.txt

你好、Jim!

我最终要使用的设置为:

DAC 采样率:1.2288GSPS

接口:16位字宽

Fdata 速率:76.8MHz

内插:16x

带宽:20MHz

Fout:500MHz

PLL:禁用

这些是实际电路板上设置的时钟和同步信号。

DACCLK (P/N):1.2288GHz

DATACLK (P/N):76.8MHz

OSR (P/N ):2.4MHz (?)

奇偶校验(P/N ):无

SYNC (P/N):无

帧(P/N ):无

Jong-min、

我让它工作了。 请尝试附加文件中的示例。

此致、

Jim

你好、Jim!

非常感谢您发送此类内容。

我设置相同的值、但输出不正常。

唯一的区别是 DAC3484、DAC3482和 TSW1400源。

TSW1400源您能否发送您所做的设置和 DAC3482EVM 寄存器值?

我将附上我的结果。

注意事项。

Jong-min、

导入的文件可能存在问题。 请使用多音调发生 器并创建20MHz 音调、然后查看是否可以按照我发送的说明从该模式获得有效输出。 获得有效输出后、我们可以专注于您尝试使用的图形发生器文件。 按照我发送的说明进行操作、如图所示。 将 GUI 设置为使用 DAC3484、而不是 DAC3482。 如果您不这样做、可能会出现问题。 加载我在 DAC3484文件夹中调用的确切配置文件。

此致、

Jim

Jim

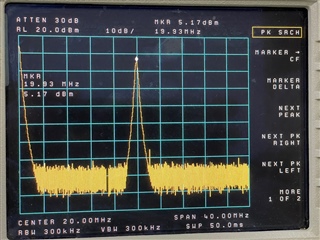

结果与您的结果不同。

我将附加该文件。

感谢您的快速回复

注意事项

你好、Jim

正如您所说、我在 HSDC Pro GUI 中将其设置为 DAC3484、并获得了如下所需的结果。 我有几个问题。

1.我正在使用 DAC3482、使用 DAC3484EVM 中保存的寄存器值是否有问题?

2.不重要、但在 HSDC Pro GUI 中设置 DAC3482是否存在任何问题?

在使用 DAC3482制造的电路板中、会发生 dacclk_Gone 警报。 在时钟源中、精确输入了1.2288GHz。

(即使清除了 dacclk 警报,也不会清除它。) 我应该检查什么?

注意事项。

请设置 FIFO 输入同步、FIFO 输出同步、数据格式器同步和时钟分频器同步源、以使用帧输入信号、而不是 OSTR。 您的 FPGA 应将该信号以及数据和数据时钟发送到 DAC。

数据速率为76.8M、数据时钟应为38.4MHz、而不是153.6MHz、因为这是 DDR 接口、帧时钟应为

fsync = fDATACLK/(n x 16)、其中 n = 1、2、…

此致、

Jim

要与帧信号同步、我是否可以在不使用同步、奇偶校验和振幅引脚的情况下仅控制帧引脚?

我正在从 FPGA 的电路板向 DAC 发送数据通信(38.4MHz)和帧(2.4MHz)、但没有任何结果。

您可以检查 DAC 寄存器吗? (只读)

注意事项。

Jong、

似乎 DAC 没有从 CDCE62005获取时钟。 确保在 J9处有一个输入时钟。确保在 CDCE62005控制选项卡上启用了 Y2。 我建议探测 R15以验证时钟是否存在。 该电阻器应靠近 DAC 的时钟输入引脚。

您还可以转到 CDCE62005控制选项卡、启用 Y4、设置分频器、并验证 SMA J10上是否有时钟。

如果一切正常、请返回到您的原始配置文件、查看您是否仍然收到此警报。

此致、

Jim

Jim。

它与 EVM 板上测试的环境相同、但结果是不可理解的。

随附了包含结果的文件。 你怎么看?

注意事项。

按照我发送的步骤、我看不到您收到的杂散(请参阅随附的)。 请确保始终以系统管理员身份运行 GUI。 否则、可能会出现一些问题。

e2e.ti.com/.../19.2MHZ_5F00_tone_5F00_1228.8MHZ_5F00_Fs_5F00_16x_5F00_int.WMF

Jim

使用 EVM 板进行测试时没有问题。 当然、我还以系统管理员的身份运行 GUI。

我有几个问题。

使用 EVM 板进行测试时、我使用 DAC3484对其进行了测试。

在 TSW1400EVM 中、寄存器值被设定并被应用为 DAC3484。

DAC3482应用于我实际设计的电路板。

是否可以将 DAC3484中设置的寄存器值按原样应用到 DAC3482?

2.您是否无法通过设置 EVM 板上的 DAC3482来检查输出?

注意事项

Jong-min、

GUI 执行配置文件中的所有写入操作时、似乎存在问题。 我看到的杂散与加载配置文件时的杂散相同。 如果我在加载配置文件后在 GUI 上发出任何命令、或在配置文件中执行一个额外的读取命令、则数据会正确加载、杂散会消失。 尝试添加了额外读取命令的附加配置文件。 这是使用 DAC3482EVM 进行的测试、输出正常。

此致、

Jim

e2e.ti.com/.../DAC3482_5F00_FDAC_5F00_1228p8MHz_5F00_16xint.txt