Other Parts Discussed in Thread: ADC12QJ1600

主题中讨论的其他器件:ADC12QJ1600

各位专家、您好!

我正在为我们的激光雷达项目评估 ADC12xJ1600、现在我有2个问题、您能不能帮助我详细了解一下? 非常感谢。

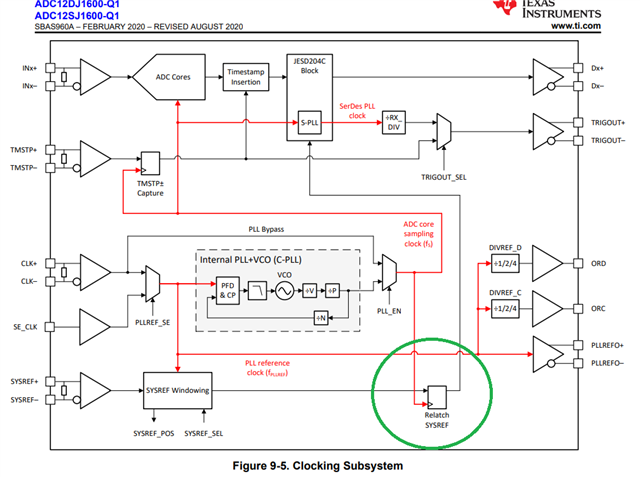

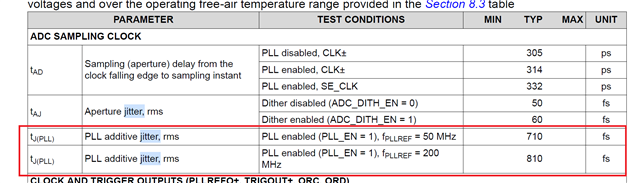

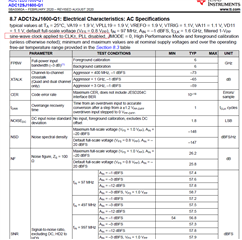

内部 CPLL 输出抖动:从 d/s 可得到大于700ps 的 PLL 附加抖动。 但对于12位 ADC@1GSPS、 我的理解是采样时钟抖动应小于200fs、以获得预期的 SNR 性能。 您能否帮助我再次确认此内部 CPLL 是否可用于此应用? 此外、您能否帮助提供12位@1GSPS 应用案例所需的详细时钟抖动或相位噪声? 如果您可以在此处帮助提供时钟设计解决方案、我们将不胜感激。 谢谢。

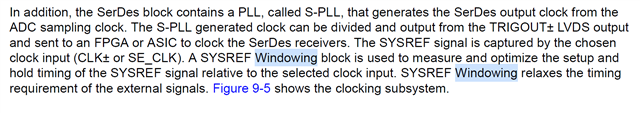

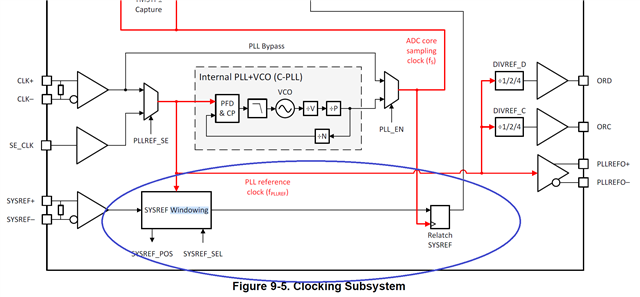

2.关于 SYNREF,如何在 d/s 中解压说明? 请在此处为我提供一个使用 SYSREF 的示例吗? 根据我的理解、同步。 来自"SYSREF 窗口化"块的时钟由 ADC 内核采样时钟重新关联、此外 、由于 PLL 参考时钟相位与内部 PLL 输出不对齐、因此如果启用了内部 CPLL、SYSREF 窗口化块似乎不起作用、对吧?

此致、

Feng

禁用 CPLL 时测量 SNR。 当 在 ADC12QJ1600 EVM 板中启用 CPLL 时、您可以帮助共享 SNR/SINAD 测试数据吗? 非常感谢。

禁用 CPLL 时测量 SNR。 当 在 ADC12QJ1600 EVM 板中启用 CPLL 时、您可以帮助共享 SNR/SINAD 测试数据吗? 非常感谢。