主题中讨论的其他器件: LMK04828

美好的一天!

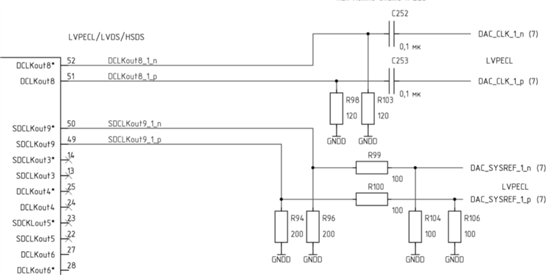

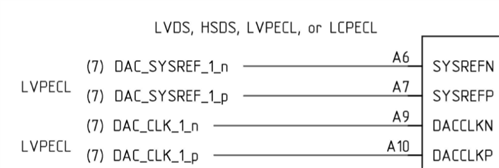

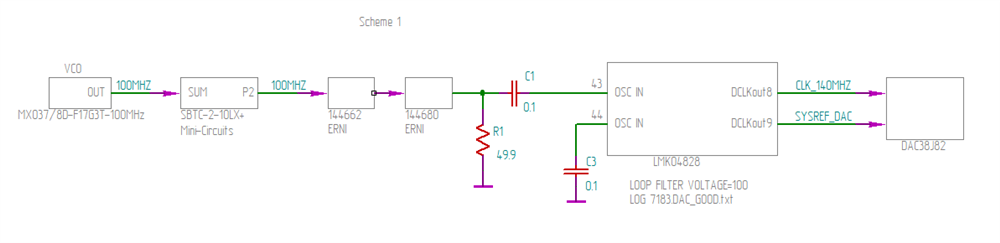

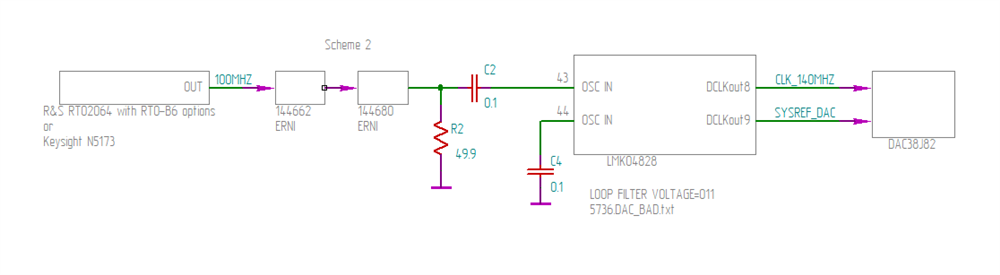

我们使用 DAC38J82、它工作正常、但有时 DAC PLL 失锁。

读取 DAC 寄存器时、差异仅在 memin_pll_lfvolt (config49)中存在、如果一切正常、则为100、如果问题是 DAC PLL、则为011。

两个值 memin_pll_fvolt 均有效。 DAC PLL 失锁的问题可能是什么?

我附加了两个带有 DAC 寄存器的文件。 DAC_GOOD.txt - DAC 工作正常、DAC_BAD.txt -当 DAC PLL 超出 lock.e2e.ti.com/.../DAC_5F00_GOOD.txte2e.ti.com/.../DAC_5F00_BAD.txt 时