主题中讨论的其他器件: DAC80504、 OPA627、

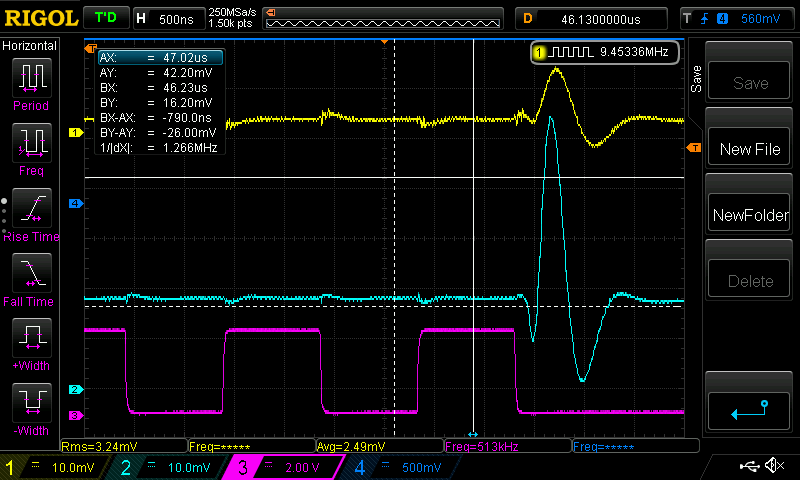

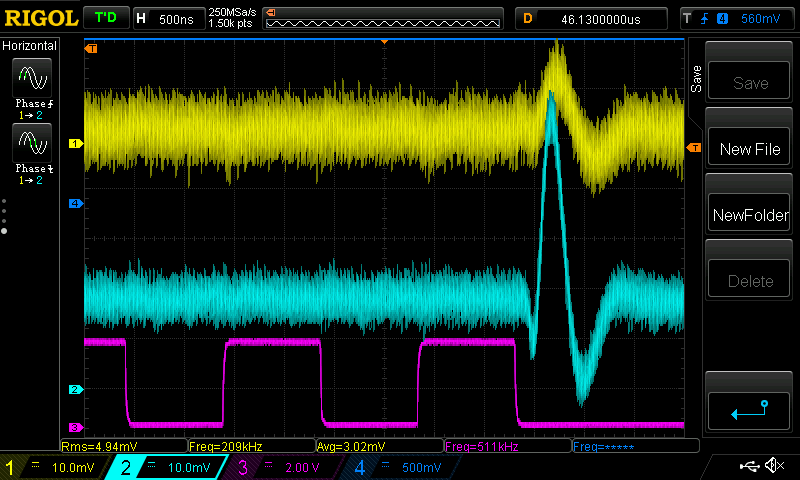

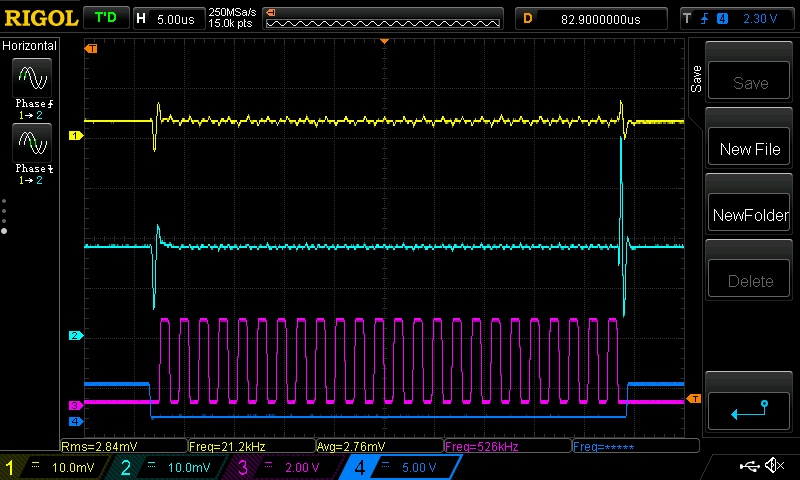

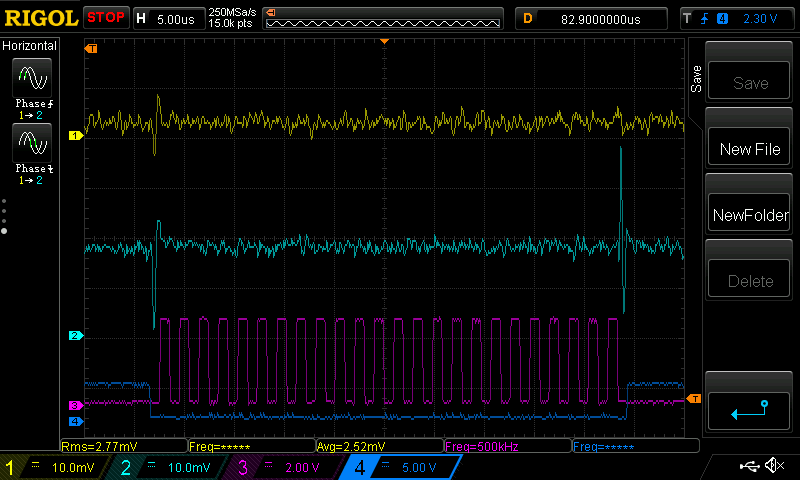

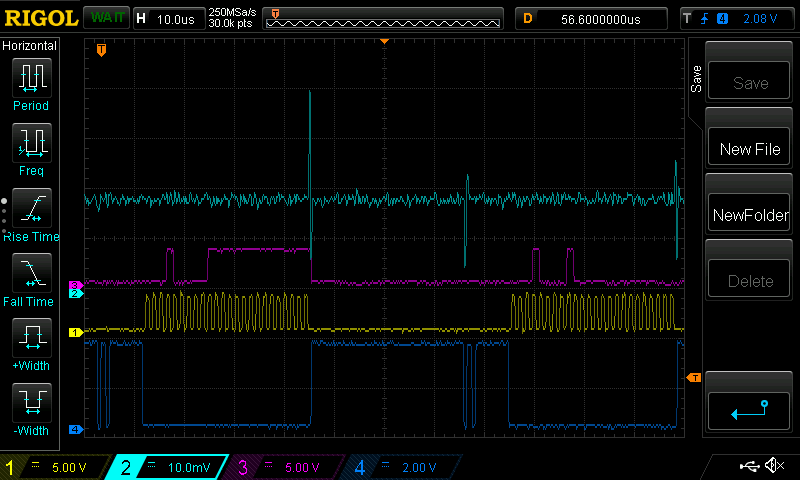

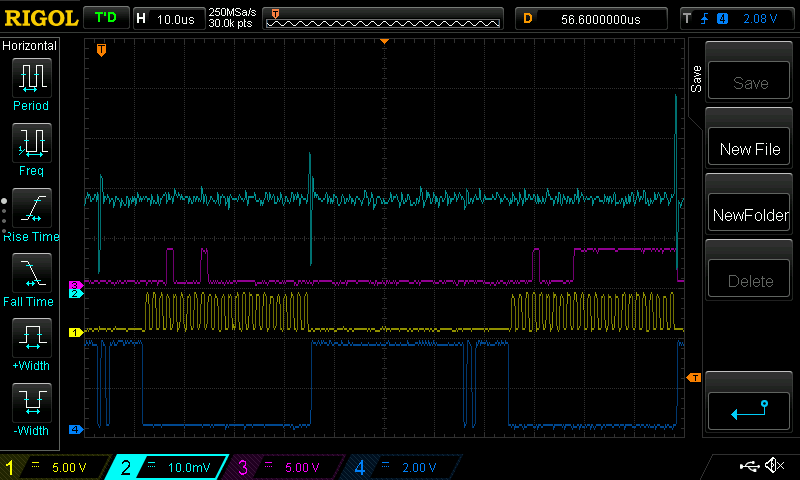

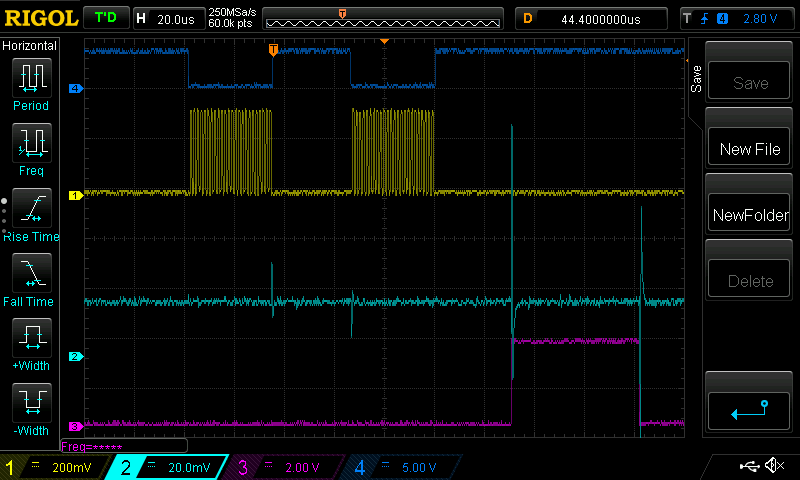

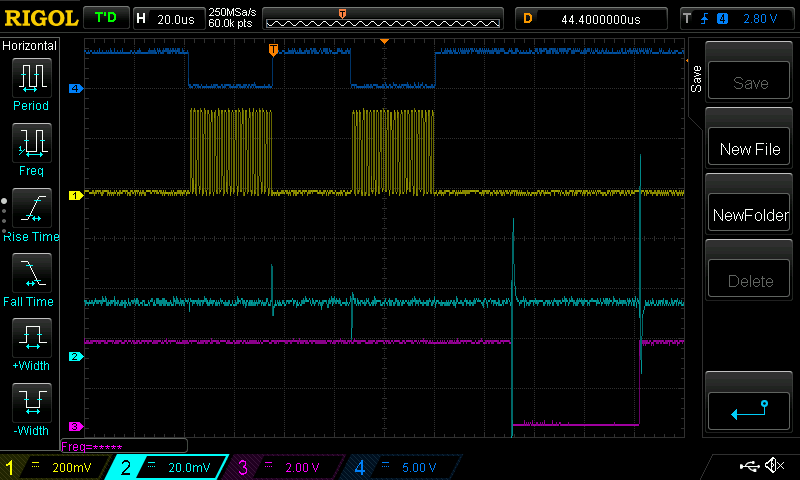

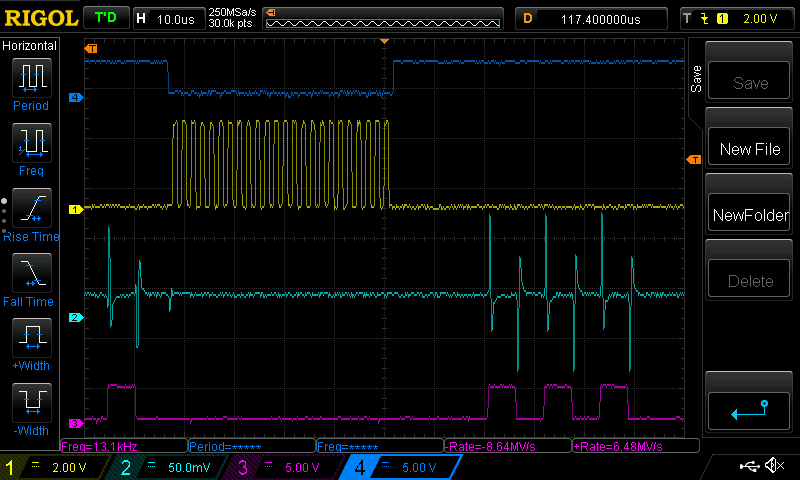

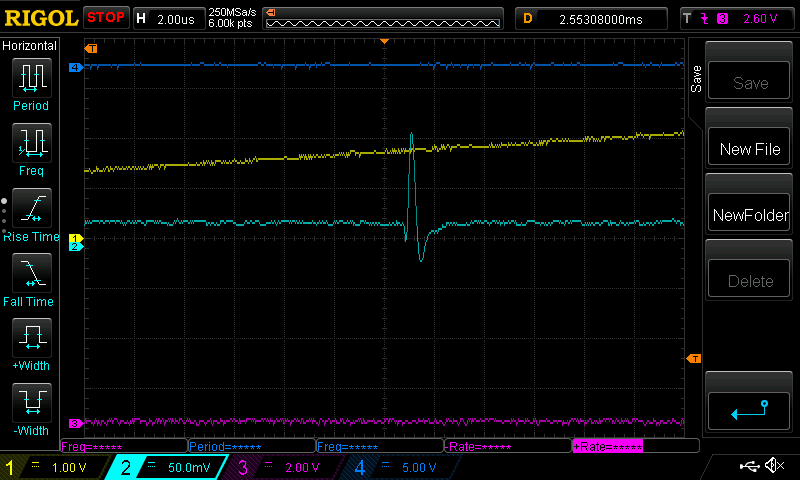

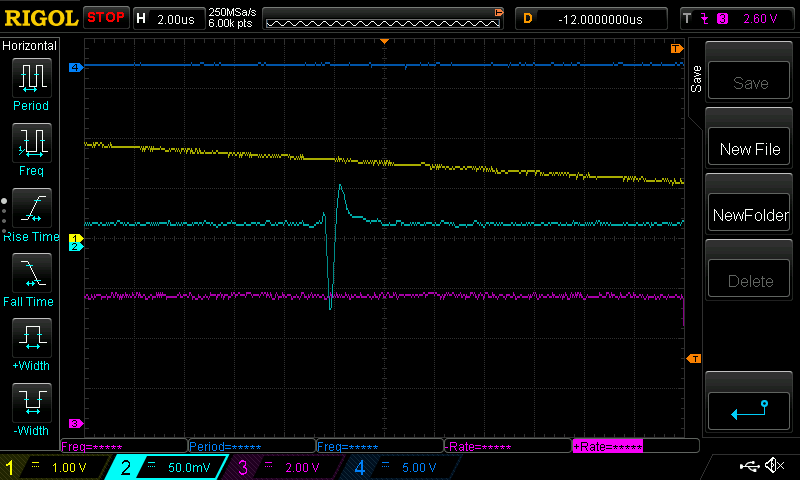

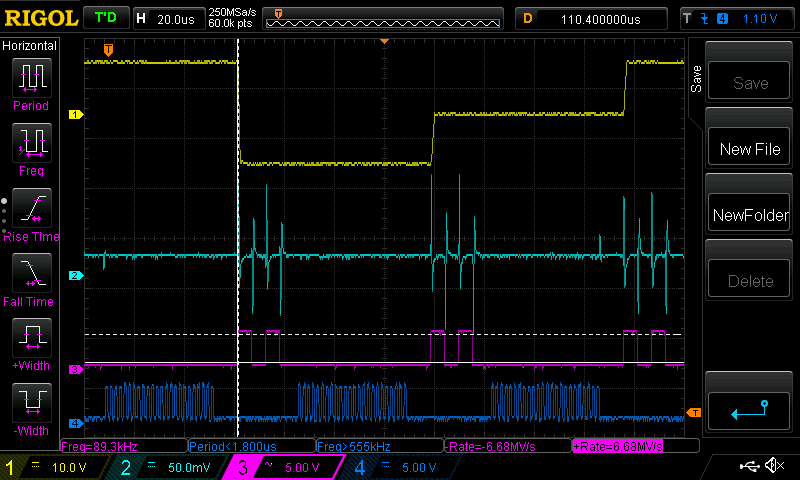

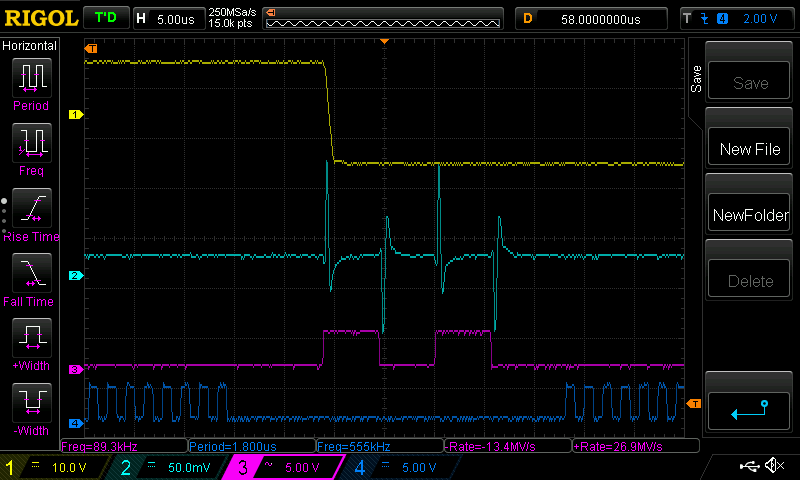

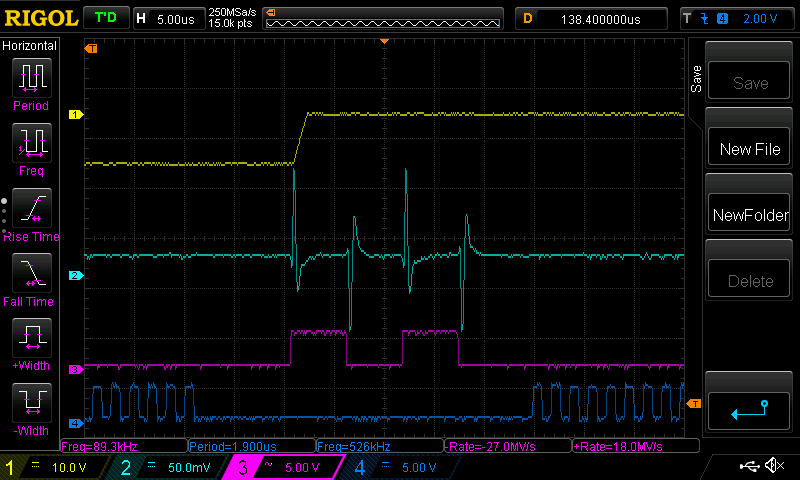

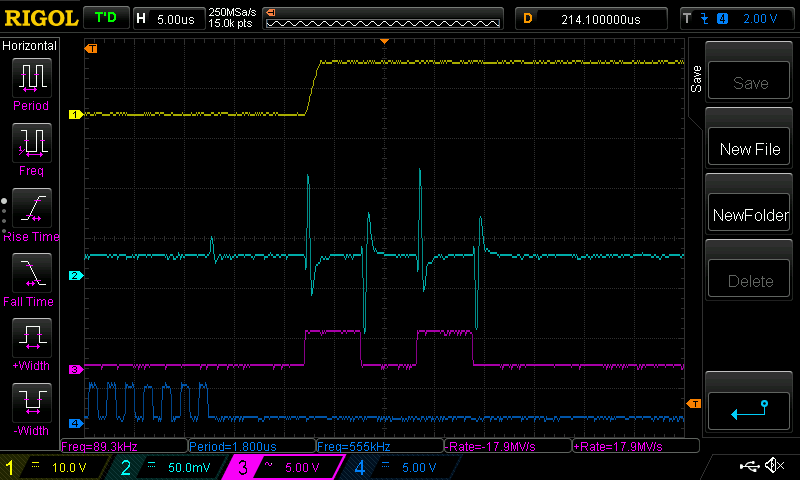

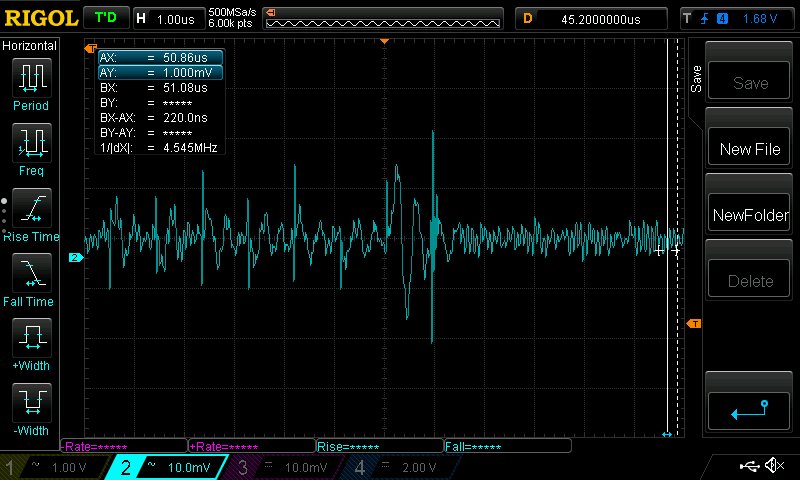

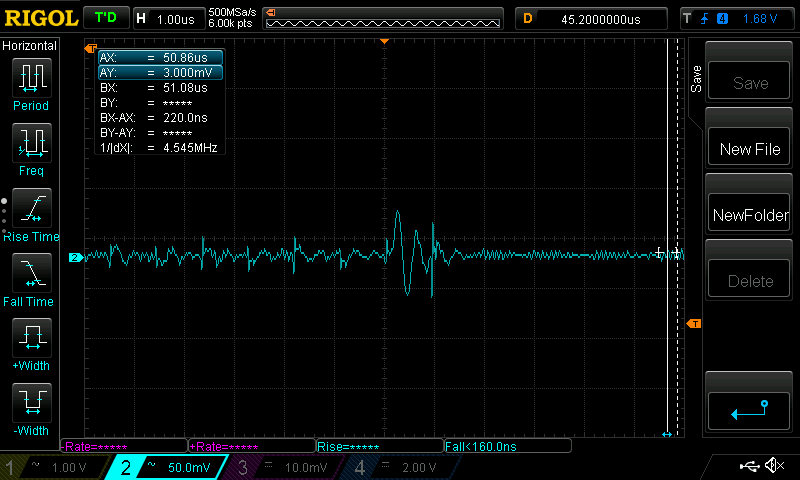

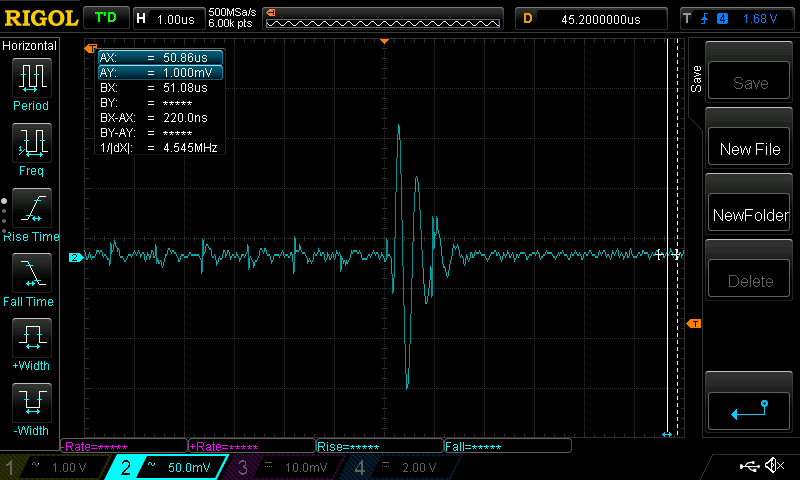

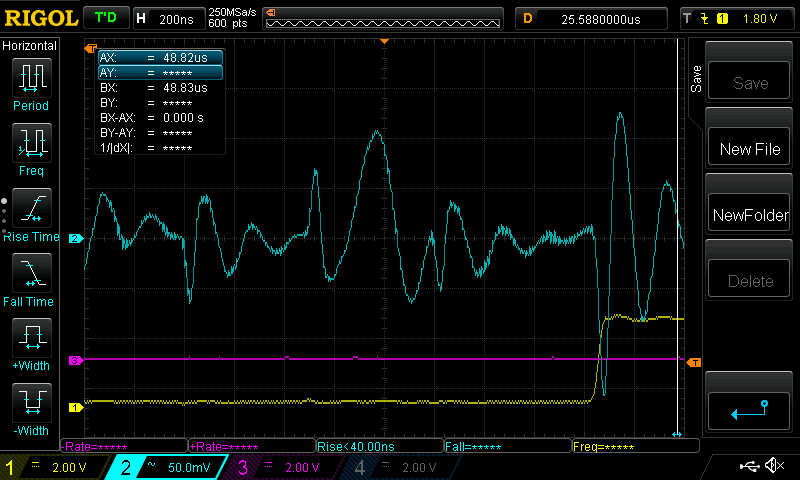

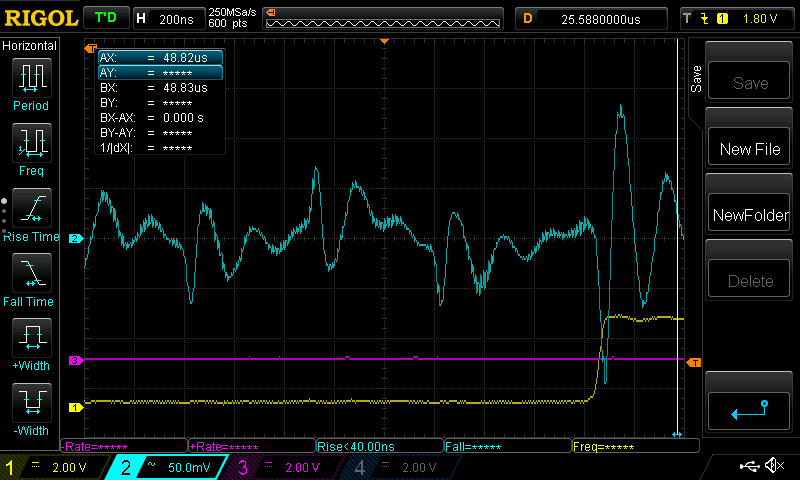

我尝试更好地理解 DAC8554上的干扰能量、因为我看到的干扰高于预期、并且不同通道上的结果也不同。 当尝试重新创建数据表中的图35时、我观察到干扰能量不是 LDAC 的函数(软或硬)、而是在数据缓冲器(而不是 DAC 寄存器)更新时发生。 此外、我在所有通道上看到相同的干扰、无论写入哪一个都是如此。 例如、如果我将通道 B 上的数据缓冲器从0x7FFF 更改为0x8000、我会看到通道 A、C 和 D 上的干扰振幅与通道 B 上的相同。这是预期的吗?

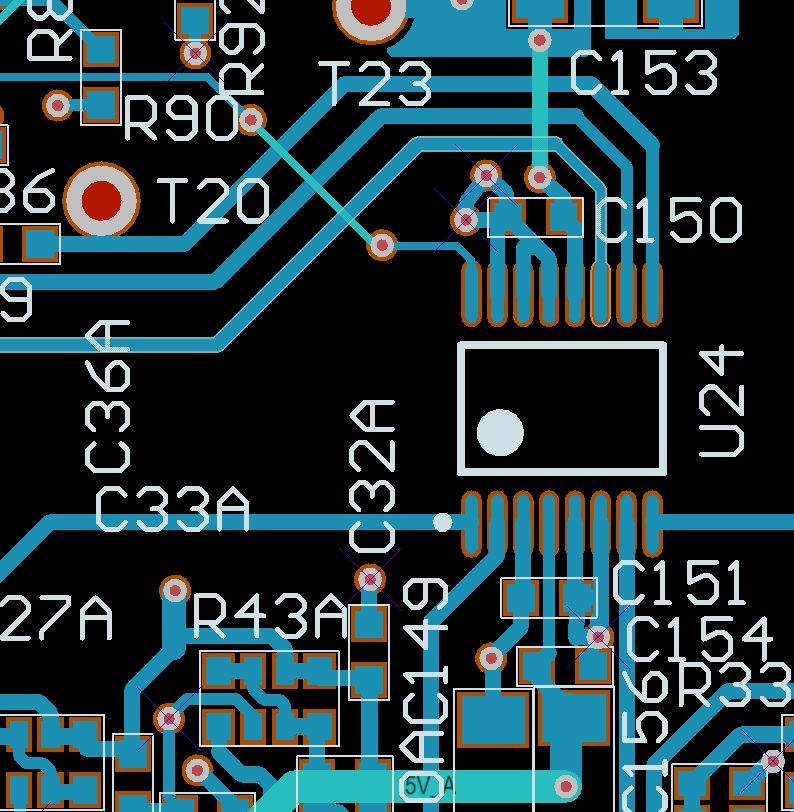

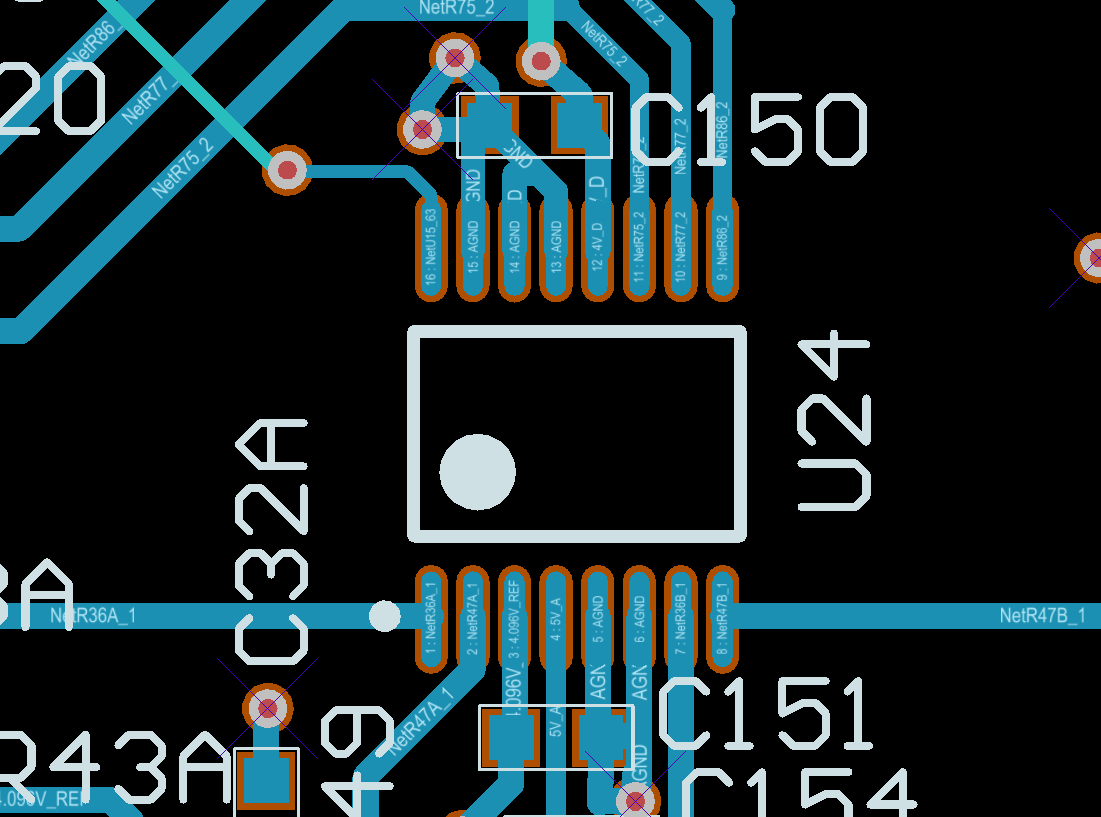

在我的电路上、我看到一些通道上的干扰能量增加。 具体而言、在更新通道 A 数据缓冲器时、我会在通道 B 上看到更大的干扰。此外、在更新通道 C 时、我会在通道 C 上看到比更新其他通道时大的干扰。 是否有任何理由期望不同通道具有比其他通道更大的干扰或对其他通道的变化更敏感的干扰? 如果这是布局问题、是否有任何布局建议可减少干扰? DAC 输出引脚上的所有毛刺脉冲、还是有其他引脚/辐射(EMI)会影响我的设计和布局?

谢谢、

本