请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS54J66 您好!

我们根据 ADS54j66EVM 制造电路板、并使用 TSW14J56对其进行测试。

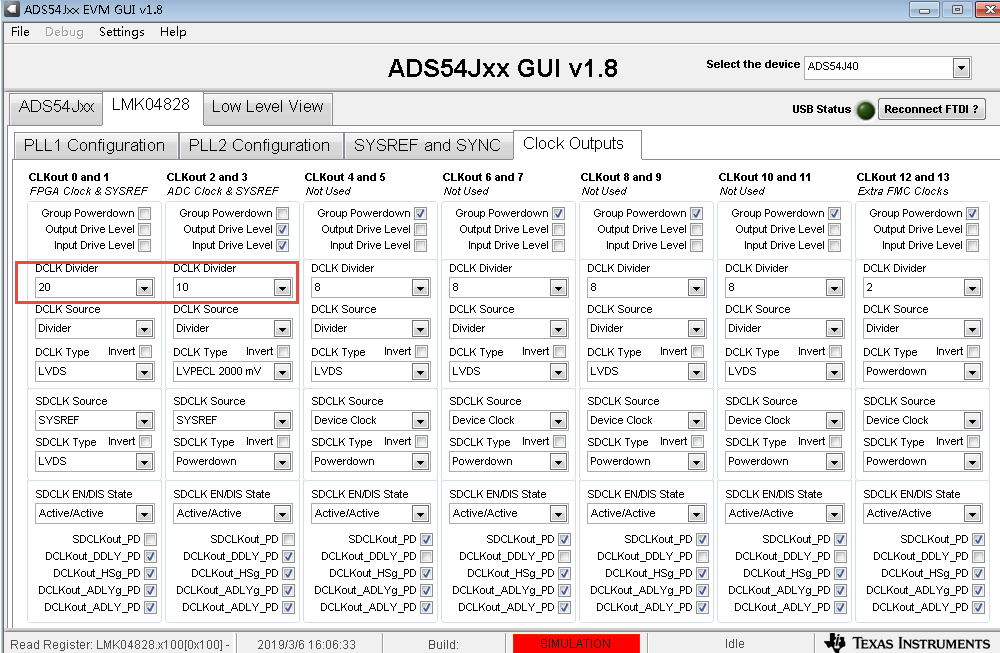

我们使用 ADS54JXX EVM 将 ADS54j66配置为模式8。

我们发现、当我们将 DCLK (到 ADC)设置为300MHz(我们更改了输出为125MHz 的 VCXO)时、JESD204B 链路将丢失。

但是、当 DCLK 分频器分别设置为12和6或24和12时、JESD204B 链路工作正常。

我们对发生这种情况的原因感到困惑。

你有什么想法吗?

此致