主题中讨论的其他器件: LMK04828、 TPS74901

大家好。

ADC:ADC12J2700

时钟:LMK04828.

FPGA : KINTEX UlteraSCALE

它具有上述配置、正在使用 Xilinx FPGA JESD204B IP。

在使用 FPGA ILA 检查 JESD204B 的 SYNC 信号时、有时会发生故障。

发生 SYNC 信号故障的条件是什么?

2. ADC 环境温度的变化是否会导致 SYNC 信号下降?

请提供帮助。 谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好。

ADC:ADC12J2700

时钟:LMK04828.

FPGA : KINTEX UlteraSCALE

它具有上述配置、正在使用 Xilinx FPGA JESD204B IP。

在使用 FPGA ILA 检查 JESD204B 的 SYNC 信号时、有时会发生故障。

发生 SYNC 信号故障的条件是什么?

2. ADC 环境温度的变化是否会导致 SYNC 信号下降?

请提供帮助。 谢谢你。

大家好

感谢您的回答。

我要按照你告诉我的方式应用它之后再尝试它。

我还有一个问题。

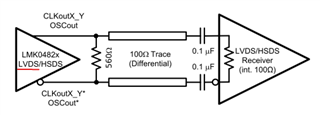

查看 ADC12J400EVM-SCH_A0原理图、可以看到传递到 FPGA 的 LVDS 信号在 LMK04828的输出端没有560Ω Ω。

当 LMK04828寄存器值设置为 LVDS 时:移除560Ω μ DMA

当 LMK04828寄存器值设置为 HSDS 时:应用560Ω μ s

以上是否正确?

Regars、

Sungdae.