主题中讨论的其他器件: ADS1278

大家好、

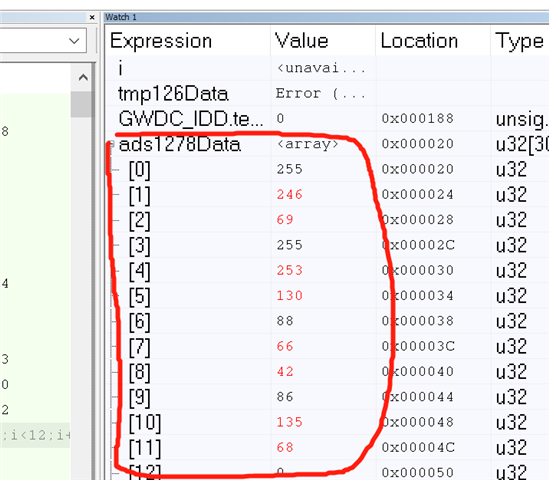

在调试 ADS1278-HT 时遇到了一个问题、即在使用 TDM 动态位置数据模式获取数据时发现不正确的数据。

下图显示了硬件连接图:

CLK 引脚连接到单片 PWM 引脚、单片发送25kHz 的方波(参见下图)、MODE0连接到 GND、MODE1在10K 时上拉至3.3V。 PWDN1至4 10K 上拉至3.3V、仅启用通道1-4。 通道1和2当前处于悬空状态。 通道3连接到振幅约为1.0V、共模电压为1.65V 的差分电压信号。 通道4的负端接板 GND、正1.8V (用于测试目的)。

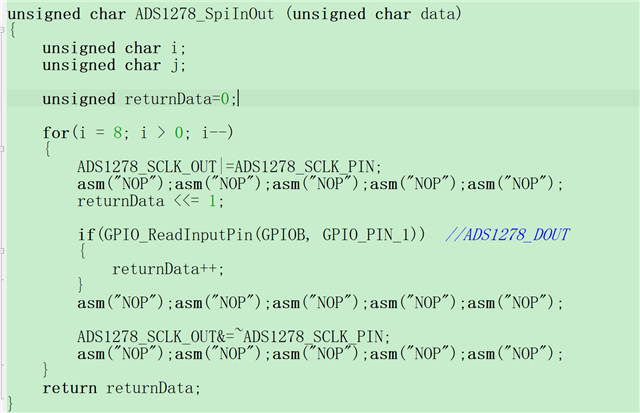

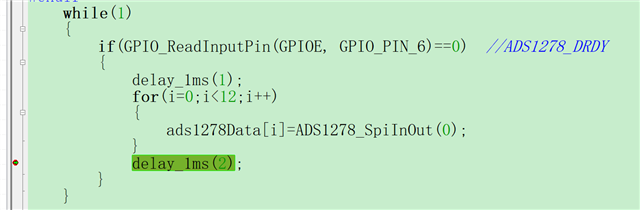

下图显示了 STM8AF 单片的 SPI 获取数据驱动器: