主题中讨论的其他器件:LMK04828、、

尊敬的 TI 专家:

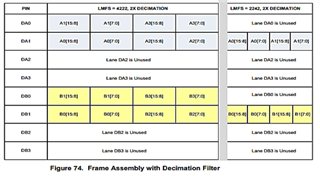

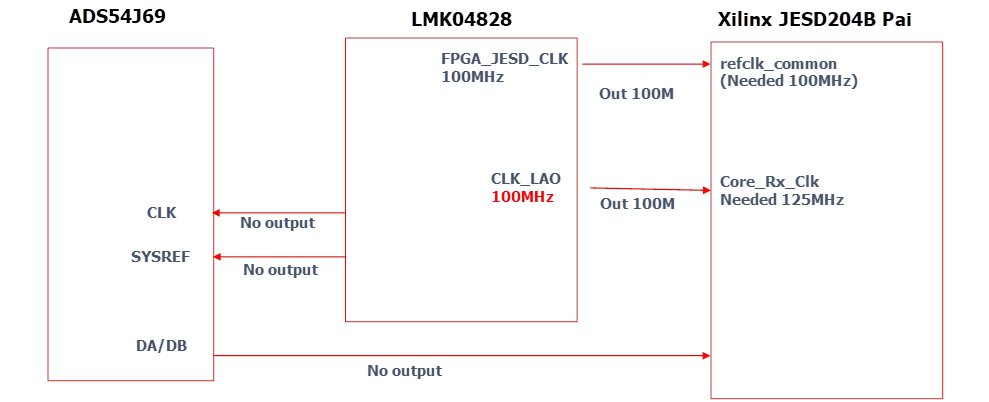

我的客户现在使用 LMK04828和 Xilinx FPGA (使用 JESD204B)测试 ADS54J69

方框图如下所示;

他们确认 FPGA_JESD_CLK 为100MHz。 (可以)

并将 Clkout 12和13 DCLK 分频器从30更改为24 ->已确认125MHz 输出。 (修复此配置是否正确?)

问题是他们无法看到 LMK04828的 DCLKOUT2和 SDCLKOUT3的输出。

附加文件是 GUI 的配置。 您能否检查设置并找到这些输出的正确配置?

如果您需要更多信息、敬请告知。 谢谢。

此致、

蔡斯