主题中讨论的其他器件: LMX2581

我们当前的产品使用的是以1.6GHz 运行的 ADC12J1600、但当我尝试通过重新配置 LMK2581和 LMK04826B 来以1.28GHz 或1.5Ghz 运行时、JESD LINK_UP 状态寄存器未在 ADC 中设置。

我需要检查或更改什么才能使 JESD 链路正常工作?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们当前的产品使用的是以1.6GHz 运行的 ADC12J1600、但当我尝试通过重新配置 LMK2581和 LMK04826B 来以1.28GHz 或1.5Ghz 运行时、JESD LINK_UP 状态寄存器未在 ADC 中设置。

我需要检查或更改什么才能使 JESD 链路正常工作?

您好、Eric、

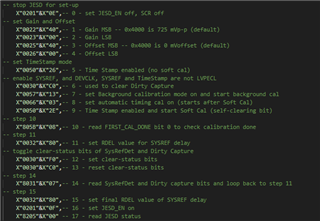

下图显示了1.6GHz 时 ADC 和 FPGA 的时钟配置:

这里是 LMX2581和 LMK04826B 的原始寄存器:

e2e.ti.com/.../2024_2D00_01_2D00_12_2D00_1600Mhz_5F00_lmx2581.txte2e.ti.com/.../2024_2D00_01_2D00_12_2D00_1600Mhz_5F00_lmk04826B.txt

ADC 的寄存器通过 FPGA 逻辑完成。

当我尝试更改 ADC 速度时、仅修改了时钟设置、而 ADC 保持了原来的状态。

此致。

男性

您好、Eric、

这是 FPGA 设计连接时钟和 ADC IC 的顶层方框图。

上电时、BOOT_CLK 允许 Clock_generator 和 Clock_distrubrutor 配置 LMX2581和 LMK04826B 以在1.6GHz 下运行 ADC。

并驱动 DEVCLK1_FPGA 生成、驱动源自系统时钟10/20/100/200/400MHz、然后触发 ADC_Interface 通过串行接口配置 ADC 寄存器。 然后 ADC_Interface 持续回读地址0x205处的 JESD_LINK_UP 状态(位6)、直到其设置。 只有这样、JESD_LANE 模块才会初始化 JESD204b 接收器。

问题:当我们将 ADC 速度从1.6GHz 更改为其他时、JESD_LINK_UP 永远不会被设置。

尊敬的 Amet:

对于 LMX2581、FPGA 代码仅写入寄存器并检查 LD 引脚是否设置为高电平。

对于 LMK04826B、FPGA 代码再次仅写入寄存器、但此时间会等待20ms 的结束标志锁定到 FPGA。 猜测这是假定 PLL 处于锁定状态并且不读取任何状态寄存器。

是的、FPGA 会检查 JESD IP 的状态、但仅报告 Xilinx JESD_PHY 内核上的位错误、因此无法启动链路。

此致。

男性

大家好、

若要使链路正常运行、Tx 和 Rx 侧都需要正常工作(具有稳定的时钟)。 请尝试以下操作:

1) 1)请检查 PHY 端的状态信号、并确保 PLL 已锁定且 PHY 复位/初始化序列已完成。 否则、Rx 将不会启动链路初始化过程

2) 2)请将 FPGA 的 SYNCn 信号添加到 ILA、并检查1.6Gsps 和其他情况之间的行为是否不同。

此致、

艾米特

尊敬的 Amet:

我可以确认 PLL (MMCME2)已锁定在 FPGA 侧、这是微火焰系统时钟启动的一部分。

JESD IP 是我们自己的 IP、由先前的工程师编写。 JESD 接收状态机尝试锁定到 CGS、但 Xilinx JESD_PHY 内核在 rxnotinable 和 rx色 散器上报告错误、这会导致其复位并重试。 我相信由于状态机不断自我复位、SYNCn 将会切换。 我将在下一次调试构建中对此进行确认。 JESD_PHY 中的数据链路速率配置不正确?

此致。

天哪。