主题中讨论的其他器件:TI-JESD204-IP、

您好!

当使用 JMODE1 (2个链路、16个通道)与 JESD204B 进行通信时、两个 JESD204 PHY IP 的 Rx_START_OF_FRAME 值异相。 这是合理的猜测吗?

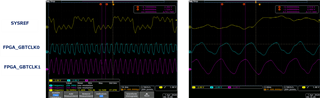

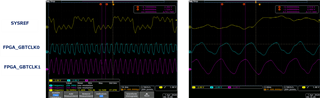

GBTCLK0和 GBTCLK1异相

两个链路(DA、DB)的帧时序似乎不同步。

GBTCLK0和 GBTCLK1用于方便 FPGA 端使用。

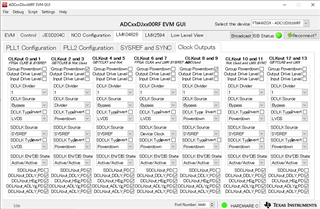

GBTCLK1被缺省输出关闭。

是否可以默认打开 GBTCLK1?

此致、

竹尾市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

当使用 JMODE1 (2个链路、16个通道)与 JESD204B 进行通信时、两个 JESD204 PHY IP 的 Rx_START_OF_FRAME 值异相。 这是合理的猜测吗?

GBTCLK0和 GBTCLK1异相

两个链路(DA、DB)的帧时序似乎不同步。

GBTCLK0和 GBTCLK1用于方便 FPGA 端使用。

GBTCLK1被缺省输出关闭。

是否可以默认打开 GBTCLK1?

此致、

竹尾市

Eric、您好!

我知道发布计划在4月底进行。

问:您目前是否正在使用旧版本的 TI IP、还是其他定制 IP?

答:我们将使用 Xilinx JESD204 PHY IP 和 JESD204 IP 或 JESD204C IP。 (这是一个评估版)我之前期待中的版本、因为 TI 的 TI-JESD204-IP 不支持 Vivado 2023.x、而且我听说下一个版本将支持方框设计。

我们正在将 TI 的 ADC 评估板与高科技 Global 的 FPGA 评估板相结合、这可能已经过实践检验。

这是我们挑战自己的地方,但它不起作用。

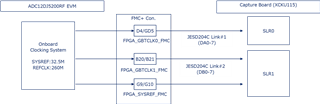

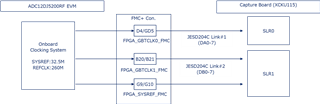

正在设置

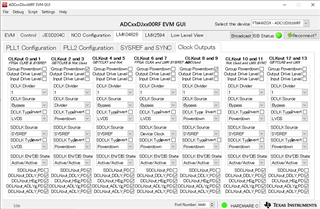

・TI - ADC12DJ5200RFEVM (可定制板载时钟选项)

・SitechGlobal - HTG830 (Kintex UltraScale XCKU115) URL:www.hitechglobal.com/.../Virtex-UltraScale-FPGA.htm

・JMODE1 (12位、单通道、2link 16通道、lanerate=10.4Gbps fpgaclk=260Mhz)

此致、

竹尾市

Eric、您好!

谢谢你的答复。

即将发布!!

>此外,我们过去没有使用这种特殊的 HTG 板,但我们已经成功的其他版本的他们的采集卡,所以我认为这不会是一个问题。

我明白了。

正如我在标题中提到的、我正在尝试解决传入数据不同步的问题。

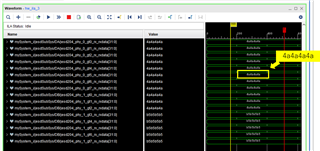

收发器的 Rx_DATA 信号不稳定。

在测试模式运行时获取了以下波形。

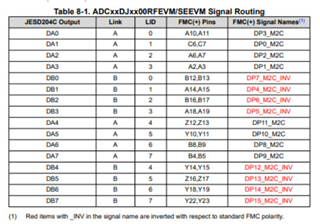

我知道 EVM 的 DB0-7位发生了翻转。

我认为数据接收侧的 FPGA 设置是可疑的、

但是、传输的数据是否可以进行位翻转?

首先、

在 FPGA 复位之后、

Regars、

竹尾市

Eric、您好!

感谢您聆听我的问题。

问:您能否分享一下您将 ADC 置于哪种测试模式?

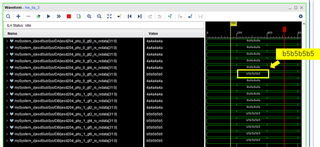

a. D21.5测试模式(JMODE1、260MHz、SamplingFreq=10.4G、LaneRate=10.4G)

问:您能否说明不同步数据的含义?

a:表明未接收到传输的数据 在 D21.5测试模式下、发送器(ADC)会发送0xB5、但接收器(FPGA)会接收到0x4A。我不明白为何有时会位翻转。 如果这些位始终反相、则可能是正负差分信号连接错误。 但是、如果位在每次移动时翻转或不翻转、这似乎不会有连接问题。 您以前可能从未听说过这样的事件。

问:所有 B 通道都反相了、这是正确的、但最好也检查您的采集卡上的此项是否匹配。

a:ADC12DJ5200RFEVM 的 B 通道至少将所有差分信号 P 和 N 都反转至 FMC+连接器。 这在 EVM 用户指南中进行了注释、而且我还检查了原理图。

8B/10B 有效字符

docs.amd.com/.../10B-Valid-Characters

如果我们观察一个8b/10b 的10位序列、如果对齐关闭了一个位、则 B5变为4A。

换言之、对齐调整是否无法正常工作?

8位10位

D21.5 => 101_10101 (0xB5) 1010_1010

D10.2 => 010 _01010 (0x4A) 010101_0101

1位移位... 010101_0101 => 1010_1010 => 0xB5

此致、

竹尾市