大家好、

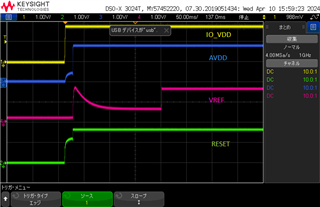

我使用具有1.6V 外部基准的 ADC3644。 我连接每个电源和 VREF 的波形。

VREF 需要一些时间才能稳定、但只要每个电源和 VREF 在释放复位之前都保持稳定、是否存在任何问题?

是否需要稍后为 AVDD 和 IOVDD 启动 VREF?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.